- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Folks,

I have a Quartus custom (no-OS) project for a Stratix IV board which works with an AD9361 daugther board. The project synthesize perfectly and I able to use AD9631 as it should be.

Now, I need to port the project to Stratix V and, of course, pinout is different. I started the project from zero adding step by step all the required Megafunctions. One specific function is the ALTLVDS_TX which I use for AD9631 transmit interface and I presume that could be the source of the problem.

The "Analysis and Synthesis" step finish without error. On the other hand, Fitter presents the following error:

Error (14566): The Fitter cannot place 1 periphery component(s) due to conflicts with existing constraints (1 LVDS clock tree(s)). Fix the errors described in the submessages, and then rerun the Fitter. The Intel FPGA Knowledge Database may also contain articles with information on how to resolve this periphery placement failure. Review the errors and then visit the Knowledge Database at https://www.altera.com/support/support-resources/knowledge-base/search.html and search for this specific error message number.

Error (175001): The Fitter cannot place 1 LVDS clock tree.

Info (14596): Information about the failing component(s):

Info (175028): The LVDS clock tree name(s): ad9361_itf:ad9361_itf_inst|lvds_adapt_tx:lvds_adapt_tx_inst|tx_lvds_ip:tx_lvds_ip_inst|altlvds_tx:ALTLVDS_TX_component|tx_lvds_ip_lvds_tx:auto_generated|pll_fclk~PLL_LVDS_OUTPUT~quadrant

Error (16234): No legal location could be found out of 4 considered location(s). Reasons why each location could not be used are summarized below:

Error (175006): Could not find path between the LVDS clock tree and destination pin

Info (175027): Destination: pin hsma_tx_d_p[5]

Info (175015): The I/O pad hsma_tx_d_p[5] is constrained to the location PIN_AD9 due to: User Location Constraints (PIN_AD9)

Info (14709): The constrained I/O pad is contained within this pin

Error (175022): The LVDS clock tree could not be placed in any location to satisfy its connectivity requirements

Info (175021): The pin was placed in location pin containing PIN_AD9

Info (175029): 3 locations affected

Info (175029): LVDS_CLK_TREE_X1_Y0_N1

Info (175029): LVDS_CLK_TREE_X1_Y107_N1

Info (175029): LVDS_CLK_TREE_X81_Y107_N160

Error (175006): Could not find path between the LVDS clock tree and destination pin

Info (175027): Destination: pin hsma_clk_out_p2

Info (175015): The I/O pad hsma_clk_out_p2 is constrained to the location PIN_G9 due to: User Location Constraints (PIN_G9)

Info (14709): The constrained I/O pad is contained within this pin

Error (175022): The LVDS clock tree could not be placed in any location to satisfy its connectivity requirements

Info (175021): The pin was placed in location pin containing PIN_G9

Info (175029): 1 location affected

Info (175029): LVDS_CLK_TREE_X81_Y0_N160

I read several posts with related information but, unfortunately, I continued clueless. Can someone explain to me what is going on and how I could possibly solve this?

This porting supposed to be only a pin exchange, shouldn't it?

Please, request more information whenever is necessary.

UPDATE:

After several iterations, the following pin assignments gives the error message:

set_location_assignment PIN_AD9 -to hsma_tx_d_p[5]

set_location_assignment PIN_AE9 -to "hsma_tx_d_p[5](n)"

set_location_assignment PIN_AB12 -to hsma_tx_d_p[7]

set_location_assignment PIN_AC12 -to "hsma_tx_d_p[7](n)"

set_location_assignment PIN_K9 -to hsma_tx_d_p[11]

set_location_assignment PIN_J9 -to "hsma_tx_d_p[11](n)"

set_location_assignment PIN_AB9 -to hsma_tx_d_p[6]

set_location_assignment PIN_AC9 -to "hsma_tx_d_p[6](n)"

Why does it work for other pins and not for the ones listed above? Are they reserved for something? Can someone shed light on this, please?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have finally found a way around. I just gave up using LVDS for Stratix V. Instead, I used CMOS and ended up rewriting the HDL. It is now working like a charm, but I still need to fix some minor issues.

With respect to the LVDS, the problem were actually the pins in different banks. It is not possible to "link together" the same clock tree for different banks.

Thanks for everybody feedback!

Best Regards.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

Check the IO pins and clock is compact to the Stratix V IO user guidelines. And also check by mistake using the transceiver pins. If using the transceiver pins , the above error will occur

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello RSree,

Thanks for your reply. What do you mean with compact to the Stratix V? Would you mind tell me what is it?

I checked assigment table from Stratix V development board. What else should I check beyond pin assigment and LVDS. I am quite sure that they are correctly assigned.

Is there anything on Megafunction properties that I should change?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The Pin assignment I mean,is that correct is it correctly assigned .By mistake it is not assigned to any transceiver pins.

If possible can you please send a sample project which makes the error so that I can comment what is the exact issue.

Re

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Here is a sample of the project which results in error. Please, let me know what are your impressions.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

I have done the below for the isolation of the issue.

- Compiled the project in 19.1 Quartus got the fitter Error.

- Made the pin assignment to auto project got successfully compiled. This means to say that the logic is fine

Next action.

Try to isolate the error which pins are making the error.

Initial the hsma_d signal is giving the error, when I try to isolate, another fitter is occurring, So I need time to understand the code and how you have initialized the code to LVDS and PLL ip. Here I feel there should have done some violation.

Let me go through it and I will update you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your help. I am looking forward to learn what is the solution. I've been looking for solutions in old posts, but I have no idea on even how to start my debugging.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

I have gone in depth to your code, the issue is with the pin assignment with the TX pins.

The issue is with the pin assignment on the LVDS Tx IP

The IO pin placement given for the LVDS Tx IP is 7B and 4B, so the clock cannot constrain ( route to both banks). That makes the fitter to fail.

Attached the screen shot of the problematic pin placement in the screen shot and also the successful compiled the project after removing the LVDS TX pin placement.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello!

Thanks for your help! Some time ago, I ended up concluding the fit would work after removing the problematic TX pins. Unfortunately, I need these pins to make my application work. The pins are required to interface with the following daughter board:

https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=65&No=946&PartNo=4

So, the TX pins has specific assignments. If I cannot assign the deleted pins then the daughter board is incompatible with Stratix V. Is that true? Is is possible to find a way around and make clock routes for both 7B and 4B banks?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I just tried to move the board to the HSMC B port. It didn't work because the equivalent pins does not have LVDS support. I followed the same numbering comparing J1 and J2 from the tables 2.40 and 2.41 (Reference Manual of Stratix V).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

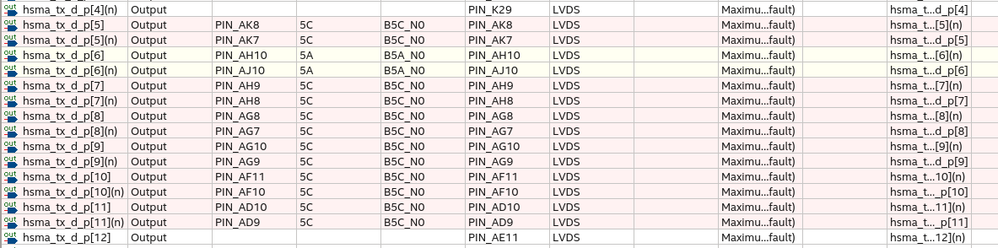

It seems the fitting works when different banks are used. I checked the Stratix IV (which the complete synthesis is success) and the pin assigment has pins in different banks for same TX bus using LVDS. Please, check the screenshot. It uses 5C and 5A banks. Why in this case there is no clock tree complaining?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

To be precise the Stratix V and And Stratix IV are having different architecture that is the reason

And to answer the above thread questions, I have a suggestion to try different LVDS IP for each bank and the clock source.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That seems a very good idea. Do you mean create a new instance just for the problematic pins? I'll try this and get back with the result...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have finally found a way around. I just gave up using LVDS for Stratix V. Instead, I used CMOS and ended up rewriting the HDL. It is now working like a charm, but I still need to fix some minor issues.

With respect to the LVDS, the problem were actually the pins in different banks. It is not possible to "link together" the same clock tree for different banks.

Thanks for everybody feedback!

Best Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have the same issue in my design. What speed were you able to get with the CMOS interface?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page