- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

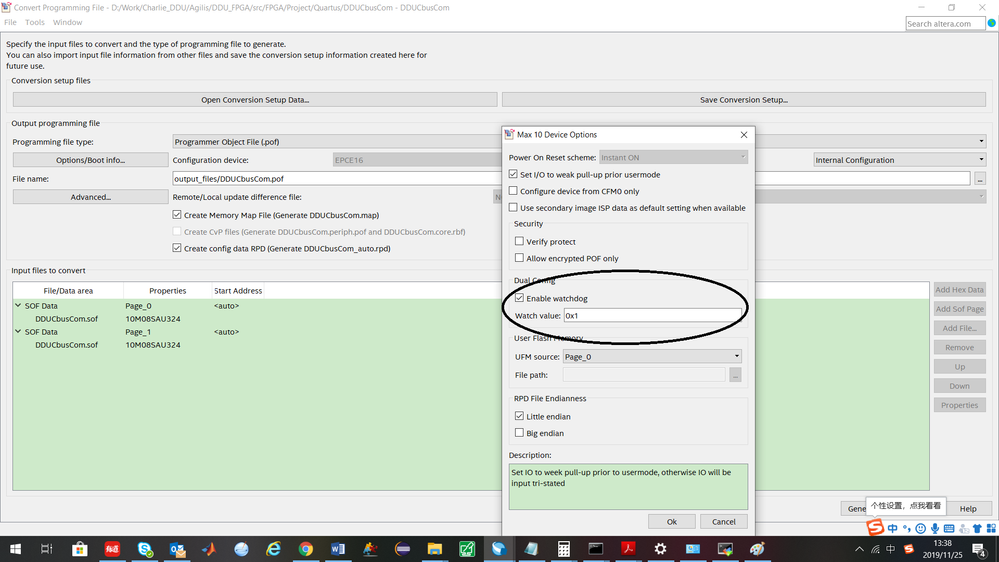

FPGA communicates with another FPGA with PHY chip. Normally(watchdog enable checkbox not checked), the PHY link led is always off when communication is good. While after I enble watchdog for dual-config(watchdog enable checkbox checked) and set watchdog value to any value, the link led will be on for about 2 seconds and return to be off. This will also be repeated after dozens of seconds. Why? How will I use the watchdog for dual-config? I didn't run remote update after power-up and the FPGA just run application firmware(just ethernet communication with another FPGA using PHY chip).

Attached file is my fpga code for the dual-config.

링크가 복사됨

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

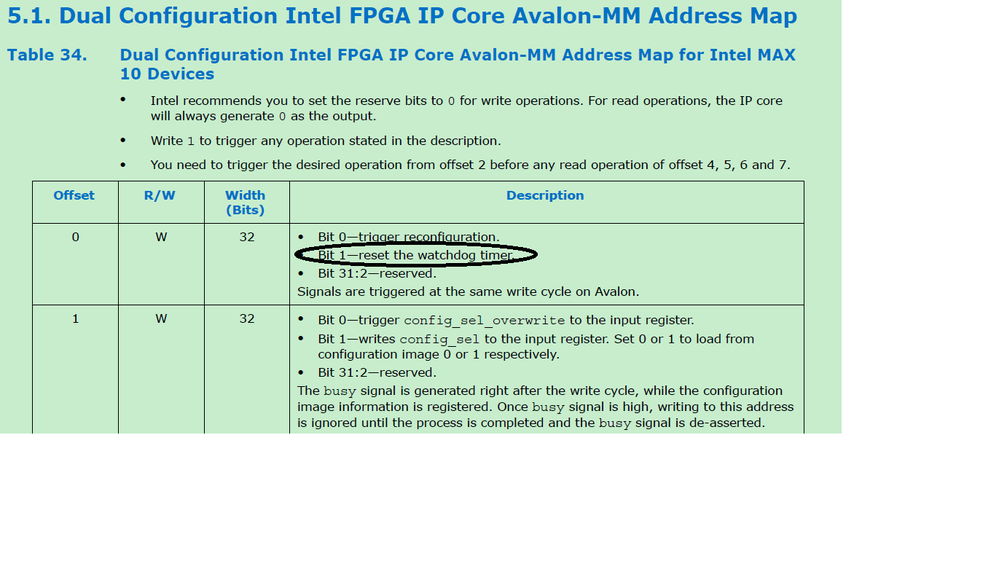

From the FPGA code, I do not observed that you performed watchdog timer reset. You will need to assert RU_nRSTIMER since you enable the watchdog timer. Please refer to table 34 in https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/ug_m10_config.pdf in order to performed watchdog timer reset

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

At the end of the code, I reset watchdog together with set reconfig by assigning sl32avmm_rcv_writedata <= X"00000003"; Is this not right?

slavmm_rcv_write <= '1';

sl3avmm_rcv_address <= B"000";

sl32avmm_rcv_writedata <= X"00000003";

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

The write data X"00000003" will assert both trigger reconfiguration and reset the watchdog timer. The write data should be X"00000002" as this will set the bit 1 reset watchdog timer only.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Will i need to reset watchdog timer frequently, or just at the time when I need reconfiguration?@JohnT_Intel

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

You just need to performed once after you reconfigure the Max 10 device.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Will the code below OK? But after write sl32avmm_rcv_writedata <= X"00000001"; then FPGA will be reconfiged, I guess FPGA will not receive reset cmd sl32avmm_rcv_writedata <= X"00000002"; How should I set reconfig and watchdog reset in my code? Thanks!@JohnT_Intel

(50Mhz clock)

when ST_DUALCONFIG_TRIGGER =>

slavmm_rcv_read <= '1';

sl3avmm_rcv_address <= B"011";

if sl32avmm_rcv_readdata(0) = '0' then

stDualConfigState <= ST_DUALCONFIG_TRIGGER_DONE;

slavmm_rcv_write <= '1';

sl3avmm_rcv_address <= B"000";

sl32avmm_rcv_writedata <= X"00000001";

end if;

when ST_DUALCONFIG_TRIGGER_DONE =>

slavmm_rcv_write <= '1';

sl3avmm_rcv_address <= B"000";

sl32avmm_rcv_writedata <= X"00000002";

when others =>

null;

end case;

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

It looks good but there is still some problem where the state machine will be reset whenever you trigger the reconfiguration. So I do not think that it will go to ST_DUALCONFIG_TRIGGER_DONE state. You will need to modify your code so that when the Application image is loaded then you will performed watchdog timer reset.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

I modified my code like below. Is this OK? But PHY communication still not work normally. Once I disable the " watchdog enable checkbox" it's OK while after enable it, it will not be OK. I reset watchdog only once at the initial state highlighted with bold character.

DualConfig0 : process( plClk )

begin

if rising_edge( plClk ) then

slavmm_rcv_read <= '0';

sl3avmm_rcv_address <= B"000";

slavmm_rcv_write <= '0';

sl32avmm_rcv_writedata <= X"00000000";

case stDualConfigState is

when ST_DUALCONFIG_IDLE =>

if slGoReboot = '1' then

if slToBeErase = '0' then

stDualConfigState <= ST_DUALCONFIG_WRWAIT;

slavmm_rcv_write <= '1';

sl3avmm_rcv_address <= B"001";

sl32avmm_rcv_writedata <= X"00000001"; -- application image(image0)

end if;

if slFaultRetrigger = '1' then

stDualConfigState <= ST_DUALCONFIG_WRWAIT;

slavmm_rcv_write <= '1';

sl3avmm_rcv_address <= B"001";

sl32avmm_rcv_writedata <= X"00000003"; -- factory image(image1)

end if;

end if;

if slWatchdogResetFlg = '0' then

slWatchdogResetFlg <= '1';

slavmm_rcv_write <= '1';

sl3avmm_rcv_address <= B"000";

sl32avmm_rcv_writedata <= X"00000002";

end if;

when ST_DUALCONFIG_WRWAIT =>

stDualConfigState <= ST_DUALCONFIG_READ;

when ST_DUALCONFIG_READ =>

stDualConfigState <= ST_DUALCONFIG_RDWAIT;

slavmm_rcv_read <= '1';

sl3avmm_rcv_address <= B"011";

when ST_DUALCONFIG_RDWAIT =>

stDualConfigState <= ST_DUALCONFIG_TRIGGER;

slavmm_rcv_read <= '1';

sl3avmm_rcv_address <= B"011";

when ST_DUALCONFIG_TRIGGER =>

slavmm_rcv_read <= '1';

sl3avmm_rcv_address <= B"011";

if sl32avmm_rcv_readdata(0) = '0' then

stDualConfigState <= ST_DUALCONFIG_TRIGGER_DONE;

slavmm_rcv_write <= '1';

sl3avmm_rcv_address <= B"000";

sl32avmm_rcv_writedata <= X"00000001";

end if;

when ST_DUALCONFIG_TRIGGER_DONE =>

null;

when others =>

null;

end case;

end if;

end process;

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

May I know what do you mean PHY communication is not working? The dual configuration and watchdog timer shouldn't impact your PHY communication. Could you check if your design is working correctly?

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Ir shouldn't influnce the PHY comminication and I also wonder why. But PHY comminication works well when I disable the watchdog. While after I enable watchdog, the PHY communication works unnormally. Every dozens of seconds the communication will be missing for around 2 seconds. It seems like the PHY is reset. But I don't know why?

And is what I modified in the code for reseting watchdog right? Thanks!

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

May I know how do you confirm if the correct image is loaded into the FPGA? Does both image will have the PHY communication work? Is there any different between the 2 image?

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

May I know if you observed PHY communication down, do you observed the image reconfigure? Are you able to check if you assert the reset the watchdog timer correctly?

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Yes, I see PHY communication down with Link LED on while it should be always off in normal situation.

The image didn't reconfigure because I didn't trigger it at all. And other parts of my code runs normally.

As to the Are you able to check if you assert the reset the watchdog timer correctly, that's what I am discussing with you and I also upload the code above 30minutes ago. So please help me see if it's OK?

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi,

The code looks goods. I just ask to double confirm in hardware but since you mention that reconfiguration is not happening is not happening then it should be fine. You will need to further debug what is actually happening that cause teh PHY communication to be down.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

It happens once I enable the watchdog , even I didn't use dual-config IP(write any code to dual-config IP). so I wonder why this can influnce PHY communication.@JohnT_Intel