- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am simulating the Soft LVDS IP core as receiver by passing a bit stream with IP core parameters configured as follows:

Power Supply Mode: Dual (for 10M50DAF484C7G)

Functional mode: RX

Number of Channels: 1

SERDES factor: 8

PLL: Internal

Data rate: 200 Mbps

Inclock frequency: 200 MHz (This value was selected automatically after I entered Data rate)

Enable pll_areset port: checked

Register outputs: checked

In the test bench I am continuously passing a bit stream (consisting 0xAA in a loop) after

- asserting the pll_areset for at least 10ns.

- checking if rx_locked has been asserted.

but the deserialized output is not consistent with the serial input. I have tried increasing the rx_inclock frequency to 400 MHz, 800 MHz and 1600 MHz but to no avail.

- Any ideas what could be the issue?

- Besides does anyone know how the inclock frequency is calculated from the data rate?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SMS.

First of all, I would recommend to look at that video - https://www.youtube.com/watch?v=02lgfcxSjQA&t=45s

It's somewhat not exactly what you are doing (14-bit shown here is more complicated), but it contents also example design which you can examine with Signal Tap and ISSP for quick iterative testing.

- Had you tried bit slip mode?

- Which clocks your internal pll generates?

- Which output data rate did you choose?

The inclock frequency depends on the output data rate (input data rate & deserialization factor).

You can check in similar IP core datasheet here - https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_altlvds.pdf

Best regards,

Ivan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

Can you check a stand alone LVPDS IP , that means mask all other logic and try the LVDS ip.

Regards,

Rs

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@IDeyn @RSree Thanks for the replies.

@IDeyn

- Yes I have tried bit slip mode. But the issue is that bitslip is not constant neither the frequency of change in bitslip. So have not been able to figure out how to do link training using the bit slip mode in this case.

- The input clock (rx_inclock) I have chosen in IP core configuration is 200 MHz. The internal PLL generates the rx_outclock of 25 MHz.

- I have tried two different data rates 200 Mbps and 16 Mbps at multiple input clock rates.

Further, during simulation, I am transmitting the serial bit stream from a testbench using a 200 MHz clock. And the same clock is being fed to the LVDS IP core, so I don't see any phase error being induced in this case. So cause of bitslip seems to be somewhere else.

@Rsree Yes I am simulating the stand alone LVDS IP core.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SMS.

The typical problem than instantiate LVDS SERDES is to confuse between FCO and DCO. Those clocks have different alignment, so SERDES result could be different because of that.

Best regards,

Ivan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have been assuming up till now that rx_inclock is DCO and rx_outclock is FCO, please correct me if I am wrong. And since FCO is generated by the IP core itself I can only control DCO and the serial data input. Given this I have tried following three cases for data rate of 200 Mbps, rx_inclock of 200 MHz and with serial input 8'hAA:

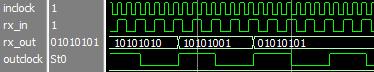

Case I:

serial data input is aligned with positive edge of DCO:

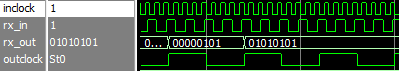

Case II:

serial data input is aligned with quarter period of the DCO:

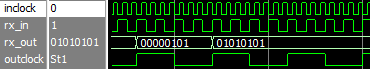

Case III:

serial data input is aligned with half period of the DCO:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SMS,

I prefer to think about FCO and DCO as outputs of, for example, ADC.

For example, you can check here -

https://www.analog.com/media/en/technical-documentation/data-sheets/AD9287.pdf Figure 2.

In that case, FCO is typically edge aligned with data, but DCO is not.

So if you will look at that manual (Figure 15. Data Realignment Timing)

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/ug_m10_lvds.pdf

you can see that here rx_inclock is aligned wth rx_in, but is slower than data change rate.

So I think in your case you better use FCO than DCO. I also will advise to assure that you have correct timing relationship between inclock and rx_in. By the way, could you try simulation as it is in Case I but trying slightly to shift inclock (less than quater period as in Case II)?

Best regards,

Ivan

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page