- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have problems, with a Arria V-Quartus 18/18.1 and time quest constraints. It seems quartus does not apply the constraints file. The same Project Works properly with a cyclone III and Q13.1.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi JOter,

What are the error messages? Could you elaborate?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

There are not errors. The problema is that the signal are delayed as spected.

The signal re: RAM_CLK (CLK) and OUTPUT 0 (counter)

We tested both signal in one scope, and we didn't notice any change between them changing the OUTPUT_DELAY constraints.

Remenber we checked it also using a C III, and in this case we got the spected signal.

We used the next constrains commands:

set_output_delay -clock vt_RAM_CLK -max [expr $RAM_tsetup + $RAM_BDb_max - $RAM_CLK_DLY_MIN] [get_ports {OUTPUT[0]}]

set_output_delay -clock vt_RAM_CLK -min [expr -$RAM_thold + $RAM_BDb_min - $RAM_CLK_DLY_MAX] [get_ports {OUTPUT[0]}]

And

set_output_delay -clock RAM_CLK -max [expr $RAM_tsetup + $RAM_BDb_max - $RAM_CLK_DLY_MIN] [get_ports {OUTPUT[0]}]

set_output_delay -clock RAM_CLK -min [expr -$RAM_thold + $RAM_BDb_min - $RAM_CLK_DLY_MAX] [get_ports {OUTPUT[0]}]

Best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you check if the constraints are being ignored under 'Ignored Constraints'? Can you provide the timing report for both design?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I send you both projects, so you can obtain all information.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi JOter,

I checked the AV_OUTPUT_DELAY_TEST using Timing Analyzer, the output delay is as what we set in the .sdc file.

max 3ns and min 2ns.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your answer.

The problem is when we checks the ouput signal whith one oscilloscope, the output delay between both signals doesn't change using differents

Best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you mean that the result in Timing Analyzer is different from the hardware result?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, the results seems to be the same independently of the constrains assignement.

Best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

What is the value in the hardware?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I haven't the numeric results, we didn't anotate them. We tested it with wide range of data output delays (for example from 0 to 8ns)

You must take into acount that the same project works properly with a cyclone III and Q13.1. So we are looking for a problema in our "Q18 and Arria V" Project, or in Q18 compiler.

Best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm sorry but I didn't see your message. At the end I didn't use any "output_delay", I only used the clock phase shift.

I try to summarize the case. I used the next configuration:

create_clock -name PSRAM_CLK -period 16 [get_ports {PSRAM_CLK}]

create_generated_clock -name vt_PSRAM_CLK -source [get_ports {PSRAM_CLK}] -divide_by 1 -multiply_by 1 -phase 180

set_output_delay -clock {vt_RAM_CLK} 2 [get_ports {RAM_A* }]

Signal meaning:

PSRAM_CLOCK: RAM mem. clk generated in a FPGA-PLL

RAM_A: RAM mem, addr.I

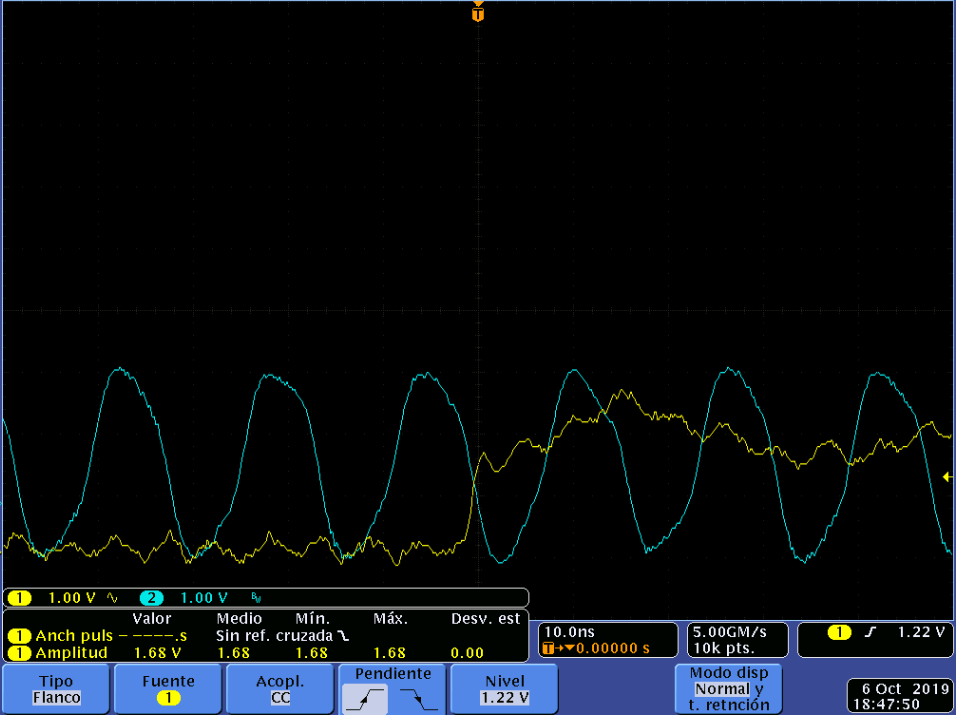

Both signals were monitoring with one oscilloscope. The delay between both was almost constant for any "set_output_delay" value, quite different to the programmed value.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page