- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

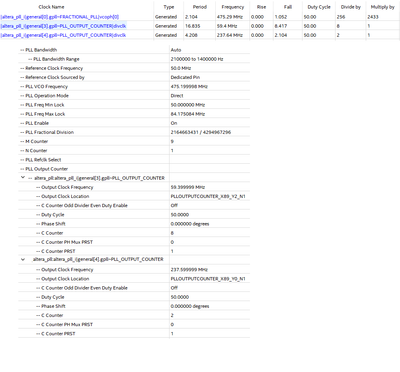

We have seen that it is different the clock configured/generated by Fractional PLL and the generated by the timing analyzer.

They use different factor to generate VCO frequency:

refCLK x (M+f/2^32) / N

For the example in the figure: (9+2164663431/4294967296) / 1 = 9.50399997993372380733

refCLK x M' / N'

For the attached in the figure: (2433 / 256) = 9.50390625

Those figures are: timing report (clocks) and fitter (pll usage summary)

How can we manage it?

What is the correct frequency?

What frequency use the timing analyzer?

Quartus Prime 18.1.1 + Cyclone V

Regards,

JMedi

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I will get back on this query.

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I got some information from our team:

The Timing Analyzer numbers do have some inaccuracies, though they are consistent with each other & don't explain the PLL report's numbers:

- Timing Analyzer stores clock periods, not their frequencies

- Periods are only stored to three decimal places

- The period of descendant clocks uses the mult & div factors of all of its ancestors, instead of using the mult & div factors of the truncated period of a parent clock

Regards.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page