- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

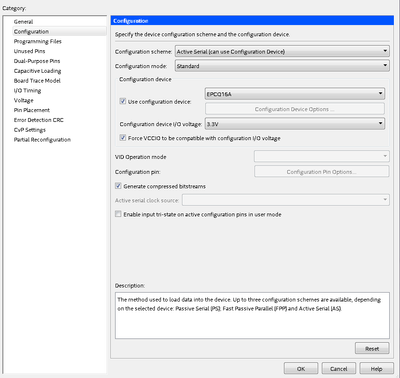

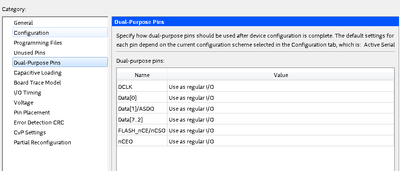

I am using Cyclone 10 device 10CL040U484. How do I assign the EPCQ configuration pins as Input or Output? Are these automatically configured based on Quartus settings (Active serial configuration)?

What should be the settings for Active serial configuration (using EPCQ16A, for ex) for the following pins?

What about JTAG pins? Should I configure them in Pin planner?

Is there any setting where I should enable JTAG?

Thank you! Your answers and suggestions are highly appreciated.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for contacting Intel community.

Kindly refer to Cyclone 10 LP pin connection guidelines and handbook.

Pin connection guideline: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/dp/cyclone-10/pcg-01021.pdf

Let me know if you need further assistance.

Regards,

Aiman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you! Reading it and proceeding with schematic design.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page