- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

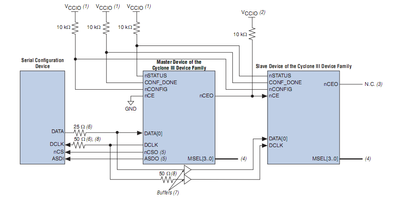

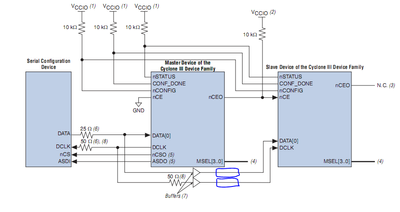

I have two Cyc III devices (master-slave, AS and PS respectively) + EPCS16 flash.

In both devices I have ROMs (megafunction), one in the master and two of them in the slave. All ROMs are initialized with .mif files.

The problem is: the slave ROMs are always broken, i.e. have bit errors, which can be seen in the In-system memory content editor (and also have bad CRC, which is calculated by the external CPU).

I can re-write content of ROM with ISMCE, and there are no errors then.

If slave is loaded from EPCS - there are errors.

If I try to reload slave via JTAG - there are errors.

I get no errors from quartus, not when programming EPCS, nor while JTAG operations. ROM megafunction themselves works correctly, i.e. I can read content of ROMs with external CPU with no problems, but content itself is broken.

Master is always working correctly - no errors, CRC is ok etc.

Connection is as shown in handbook, I also have 2 buffers on the DCLK and DATA[0] lines (74LVC1G125), but no series resistors (they are optional for 3.3V, according to handbook). Trace length from buffer to slave is about 110..120 mm.

Appreciate for any help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think I've found the problem.

There is a trace connected to pin 76 on the master and pin 99 on the slave. Trace is pulled up to 3.3V via 2.2k

This **bleep** resistor was dead, and the trace was actually floating.

I didn't use this pins before, so I can't reveal the resistor is dead.

As I start to use it, all logic became a total mess. Something worked, something not. By elimination I found the culprit.

I can't explain how this trace connected with loading errors (when FPGA not even in user mode), but the fact is - replacing resistor solved all problems, ROMs working now (though I don't use them anymore).

Thanks to all, problem solved!

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

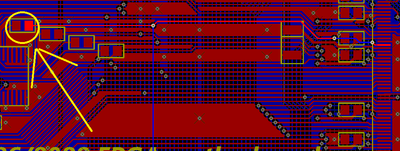

@Vic3Dexe wrote: I've cut traces and placed series resistors afters buffers (51R)

those resistors where are you connecting (data line or clk line or on both lines)

- if you see bellow attachment in schematic on clk and data lines using two different resistors in series.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@hareesh wrote:

@Vic3Dexe wrote: I've cut traces and placed series resistors afters buffers (51R)

those resistors where are you connecting (data line or clk line or on both lines)

- if you see bellow attachment in schematic on clk and data lines using two different resistors in series.

As I said in post 4:

I've tried to remove buffers and change them to zero Ohm resistors - no changes.

Then I've replaced 0R resistors to 51R ones - no changes.

Then I've put buffers back, cut traces afters them (which are facing to the slave), and put 51R there in series. No changes.

So now it's like that. Both resistors placed as close as possible to buffers.

There is no point in resistors before buffers, as the master working ok.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Awaiting access to my friend's oscilloscope (it's in use for now). Don't know when it will be avail. Maybe this week, maybe next.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Vic3Dexe,

Since there are no update from you. pls respond when can you share oscilloscope data.

Thanks,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for sharing files, just give me some time, we are working on it.

thanks,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think I've found the problem.

There is a trace connected to pin 76 on the master and pin 99 on the slave. Trace is pulled up to 3.3V via 2.2k

This **bleep** resistor was dead, and the trace was actually floating.

I didn't use this pins before, so I can't reveal the resistor is dead.

As I start to use it, all logic became a total mess. Something worked, something not. By elimination I found the culprit.

I can't explain how this trace connected with loading errors (when FPGA not even in user mode), but the fact is - replacing resistor solved all problems, ROMs working now (though I don't use them anymore).

Thanks to all, problem solved!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »