- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Intel,

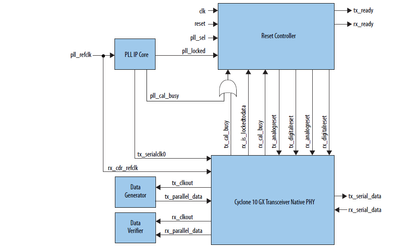

When I am learning to use SFP+ interface of Cyclone 10 GX board, I designed the project with ATXPLL IP core、Reset Controller IP Core 、Cyclone 10 GX Transceiver Native PHY, and connected them like the user guide said:

Then I use Modelsim to simulate the whole project,but I can't check the "tx_serial_data"as expected,it's always 0. Then I find the "tx_clkout" and the "rx_clkout" are always 0 ,too.But I can't check the "tx_serial_clk0" signal.

Could you help me to check the problem? Did I use the IP Core in a wrong way?

Thanks.

링크가 복사됨

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi @LTN

May I know does my latest reply helps?

Do you need further help in regards to this case?

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi @LTN

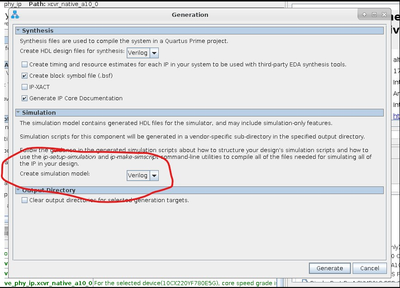

I took the design and generated the simulation models for the IP and I notice that these options were not selected by default. Is it possible that you are trying to simulate the design with the synthesis RTL? You cant do that.

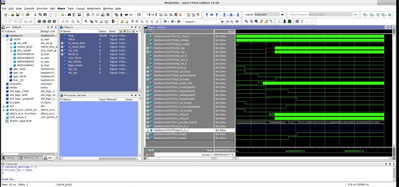

I hacked my simple testbench and simulated your project with it. As you can see it works just fine. I’ve attached the project with my testbench back to you.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

I have yet to receive any response from you to the previous question/reply/answer that I have provided but I believed that I have answered your question.

With that, I will now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi @RichardTanSY_Altera ,

I read the dynamic reconfiguration part of the user guide again, and realize that dynamic reconfiguration is related to Avalon-MM interface.Is the Avalon-MM interface necessary?

Looking forward to your reply.

Regards,

Li.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

The AVMM interface is not just for dynamic reconfiguration. It is also required for transceiver calibration which is mandatory for optimal performance. It is recommended to enable that interface.

For other unique question, please kindly file a new case. This will helps with our case analysis that we use to assess our customer support requirements. Hope you understands.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

There is my project in QuartusPro 17.1.

In this project, I enable the dynamic reconfiguration interface on the PHY, and set these interface like the example.

Then simulate the project in ModelsimStarterEdition.

The current problem remains that the tx_clkout and the rx_clkout signal is always 0.And after enable the reconfiguration interface,most of the signals are working in a wrong way now.

By the way, as you said,I post other question in a new case,why never recive any reply?

Regards,

Li.