- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have gone through the UG :Intel® Arria® 10 DisplayPort IP Core Design Example User Guide

UG-20075, and example design

In this it uses FPLL and stores calibrated link rates for different speeds. and while changing from one speed to other calibration is not required.

My query is

1)can use ATX PLL instead of FPLL ?

2)Does ATX Pll supports storing link rate feature ? without using Multiple Reconfiguration Profiles!

----------------

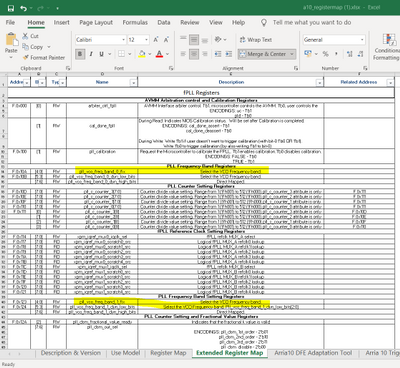

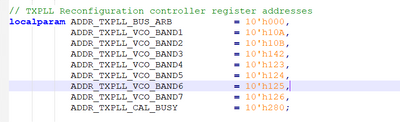

In display port design for FPLL is used, which having registers to store the frequency band, the similar registers are not available for ATX PLL.

SNAPSHOT FROM A10 register map excel sheet.

I need to figure out whether i can use the existing logic from display port for switching speed when i use ATX PLL without re calibrating after changing speed?

----------------

These registers are available in FPLL section, and these are used for storing link rate and load back the link rate,

can these registers will work for ATX PLL too ?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Pls see my comment below

- Can use ATX PLL instead of FPLL ?

- Yes. You can use ATX PLL instead of fPLL but may I know the reason why you want to use ATX PLL ?

- ATX PLL is typically used for 10G and above application while Arria 10 DP 1.4 only support till HBR3 which is only 8.1G. You don't really need ATX PLL

- Does ATX Pll supports storing link rate feature ? without using Multiple Reconfiguration Profiles!

- Basically DisplayPort example design is unique design where Intel Engineering team implement the design in a way that access a lot of PLL internal register setting.

- While for external user, it's recommend to just use the PLL reconfiguration profile to change to different PLL clk frequency and let PLL IP handle the PLL internal register setting automatically. User shouldn't mess up with PLL internal setting unless you know exactly how to tweak it like Intel Engineering team.

In short, I strongly recommend you to use back the fPLL and reconfig controller design in DisplayPort example design to ease the pain of design implementation detail as it's quite complicated in nature

- I won't be able to advise you further on how to tweak these internal setting as well

Thanks for your understanding

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI @Deshi_Intel

< You can use ATX PLL instead of fPLL but may I know the reason why you want to use ATX PLL ? >

I want to use the same logic but not for DisplayPort, My speeds are 5G,10G,10.3125G so i am using ATX Pll.

<I won't be able to advise you further on how to tweak these internal setting as well>

Ok, confirm me that ATX PLL is also can be supports Pre-calibration feature!

Thanks&Regards,

Rajesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Oh, I didn't realized you are not using DisplayPort IP and in fact targeting other application.

- Yes, you need ATX PLL if you are running 10G.

- ATX PLL should be able to achieve similar pre-calibration operation as both fPLL and ATX PLL also support reconfiguration profile

Just curious why you need pre-calibration feature ?

- This is unique for DisplayPort protocol only to shorten the Protocol link up time

- For other protocol, normally you can perform transceiver or PLL calibration later once you enter into FPGA user mode.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just curious why you need pre-calibration feature ?

Our application requirement is to change speed dynamically

for " Multiple Reconfiguration Profiles" i may have to calibrate after changing speed every time.

to save the calibration time i found pre calibration used in DisplayPort is efficient.

Regards,

Rajesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the clarification. I see your point now but this is not the recommended design practice.

- It's recommended to always recalibration either the PLL or the transceiver channel depends you are modify which block to change speed

- So that you get the most accurate internal analog setting tuned for your application current voltage and temperature condition

The pre-calibration feature in the DisplayPort example design is forced to be done to shorten the Displayport link boot time time. This is one outlier case here.

For your case, I suggest you to follow the recalibration process after changing speed as per guideline in Transceiver PHY user guide doc.

Thanks.

Regards,

dlim

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page