- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In the post

it is stated that

"When using dedicated SERDES circuitry, it does not support differential SSTL IO standard. The SERDES requires a direct connection to I/O and hence it can only interface to true LVDS I/O. So, please change IO standard of TX pins to LVDS."

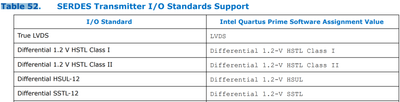

This statement conflicts with table 52 of Intel Cyclone 10 GX Core Fabric and General Purpose I/Os Handbook (https://www.intel.com/content/www/us/en/programmable/documentation/vua1487061384661.html), which explicitly states that SERDES Transmitter I/O Standards Supports diff SSTL-12 (please see the follow screenshot).

Could you please clarify?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The maximum achievable I/O frequency is different for each I/O standard and is depends on design and system specific factors. Ensure proper timing closure in your design and perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

Thank you

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

1) The IP is for LVDS only. The name itself is LVDS SERDES Intel FPGA IP. So it supports only LVDS.

2) The restriction arises because it mentions that it requires true differential I/O standard. Only LVDS support that

3) Section 5.6.3 does not say about the dedicated circuitry.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your reply.

As you said, the LVDS SERDES IP supports only LVDS. How does Cyclone 10 GX general-purpose support 1.434 Gbps differential SSTL-12 (https://community.intel.com/t5/Programmable-Devices/Does-Cyclone-10-GX-general-purpose-support-1-434-Gbps/m-p/1287593)? I need to transmit 1.434 Gbps data in diff SSTL-12. I cannot use LVDS because the common mode voltage of LVDS is not compatible with the data receiver.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The maximum achievable I/O frequency is different for each I/O standard and is depends on design and system specific factors. Ensure proper timing closure in your design and perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page