- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

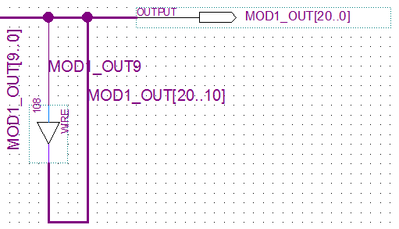

I used create/update option in Quartus 18.0 to generate a VHDL file from a schematic:

It is a sign extension operation where MOD1_OUT[9] is extended to convert 10 bit vector to a 21 bit vector. The equivalent VHDL code generated for this block is quite surprising.

SIGNAL MOD1_OUT_ALTERA_SYNTHESIZED : STD_LOGIC_VECTOR(20 DOWNTO 0);

MOD1_OUT_ALTERA_SYNTHESIZED(20 DOWNTO 10) <= (MOD1_OUT_ALTERA_SYNTHESIZED & MOD1_OUT_ALTERA_SYNTHESIZED & MOD1_OUT_ALTERA_SYNTHESIZED & MOD1_OUT_ALTERA_SYNTHESIZED & MOD1_OUT_ALTERA_SYNTHESIZED & MOD1_OUT_ALTERA_SYNTHESIZED & MOD1_OUT_ALTERA_SYNTHESIZED & MOD1_OUT_ALTERA_SYNTHESIZED & MOD1_OUT_ALTERA_SYNTHESIZED & MOD1_OUT_ALTERA_SYNTHESIZED & MOD1_OUT_ALTERA_SYNTHESIZED);

But I think the right way of expressing this sign extension would be:

MOD1_OUT_ALTERA_SYNTHESIZED(20 DOWNTO 10) <= (MOD1_OUT_ALTERA_SYNTHESIZED(9) & MOD1_OUT_ALTERA_SYNTHESIZED(9) & MOD1_OUT_ALTERA_SYNTHESIZED(9) & MOD1_OUT_ALTERA_SYNTHESIZED(9) & MOD1_OUT_ALTERA_SYNTHESIZED(9) & MOD1_OUT_ALTERA_SYNTHESIZED(9) & MOD1_OUT_ALTERA_SYNTHESIZED(9) & MOD1_OUT_ALTERA_SYNTHESIZED(9) & MOD1_OUT_ALTERA_SYNTHESIZED(9) & MOD1_OUT_ALTERA_SYNTHESIZED(9) & MOD1_OUT_ALTERA_SYNTHESIZED(9));

Could anybody tell me if this is a bug in code generation? Are there any other known issues in VHDL generation from schematic file? Is the naming format MOD1_OUT9 a right way to name the 10th bit of the vector?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

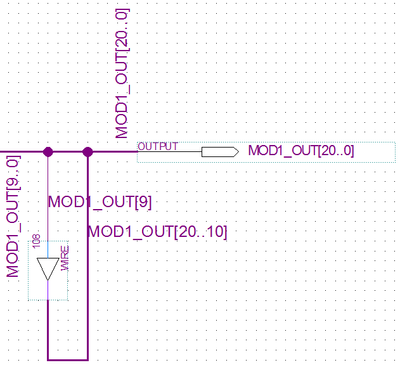

I'm not sure what you're doing there (it looks like a short circuit), but individual signals in the schematic editor must have the bit in square brackets: MOD1_OUT[9].

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I changed the name to MOD1_OUT[9] (with square brackets added) as shown below. But no change in the generated code.

And this is not a short circuit. It is just extending the MSB of a 10 bit vector to generate a 21 bit vector output. But the VHDL code generated is concatenating the complete vector "MOD1_OUT_ALTERA_SYNTHESIZED" instead of concatenating only the 10th bit "MOD1_OUT_ALTERA_SYNTHESIZED(9)". I encountered similar issues in other schematic files as well.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page