- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everybody!

I’m working on Arria 10 SoC and I want to verify it is possible to reset the HPS from the FPGA design (per state machine in the FPGA) and to verify it is possible to load the FPGA in a way HPS reboot will not stop the FPGA – need to understand the procedure of doing so.

Any information is appreciated.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

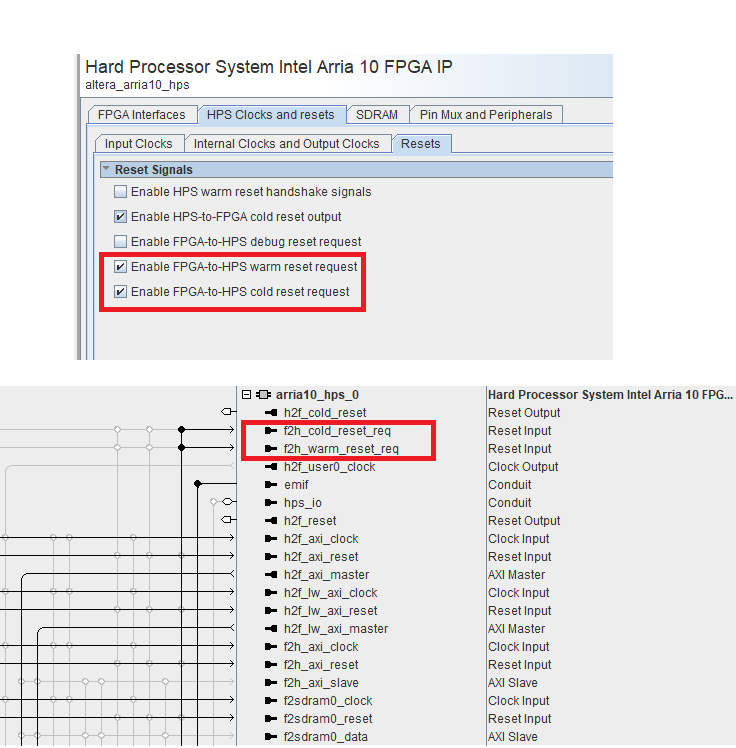

You can configure this in the parameter editor for the HPS. You just enable the signal from the FPGA to reset the HPS. I forget what the parameter is called, but look at the reset control options. As to the second part of your question, think of the device like two separate chips. They can interact with each other through control signals and the highspeed and lightweight busses, but the state of one is not reliant on the other. Resetting the CPU will not affect the FPGA's operation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @sstrell ,

For my first question I could see the options as you mentioned in your post and I enabled to use it, but how can I control these reset signals from FPGA design. Could you please brief on this by giving some real-time example?

Coming to my second question, I need to understand how h2f_reset (in my design this acts as hard/soft reset) will affect FPGA fabric though it is not connected to any FPGA IPs.

Please clarify.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You have the f2h resets connected, what you're highlighting in your screenshot. To use them, just enable reset from some logic on the FPGA side, whatever you have connected. Or export them out of the Platform Designer system and connect them to other control logic. They're just control signals, nothing fancy. Of course, go through the HPS documentation to understand what gets reset in the HPS for either cold or warm reset.

For h2f reset, this is a reset you would connect up to your FPGA design (you already have it exported out of the system in the screenshot) and control through software running on the processor, either bare metal or higher up (application running in Linux perhaps).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @sstrell ,

Thanks for the update. Now I can able to reset the HPS from FPGA using some control logic but the problem is when I reset the HPS, it will start to reboot and rewrites the periph.rbf and core.rbf again as many times we reset. But my requirement is to reset only HPS not FPGA (rbf files should not rewrite). How can I achieve this ? Any information on this will be appreciated.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So you have an HPS boot-first scenario set up and it's trying to reprogram the FPGA on reset. I'm thinking that a warm reset of the processor (instead of cold) would prevent this, but I'm not sure. You'll need to go into the HPS parameters and make adjustments (don't have it open right now so I can't tell you what to change) and regenerate the bootloader.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @sstrell ,

Tried with both warm and cold resets but nothing seems to work. Anyway is it possible avoid reset of FPGA DDR when HPS reset is issued ?

Because when I write some data to FPGA DDR and read after reset in uboot or reboot in kernel, it will be erased and reads back as 0x0.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can configure your FPGA as standalone and not from HPS. In that way, warm and cold reset will not affect your DDR memory.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page