- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are using ALTLVDS_RX to receive high-speed serial data in our design. We have been successfully using this design with 400 MHz input clock (800 Mbps) for a while.

We are now trying to use the same design with 300 MHz input clock (600 Mbps) but are seeing sporadic CRC errors in out data.

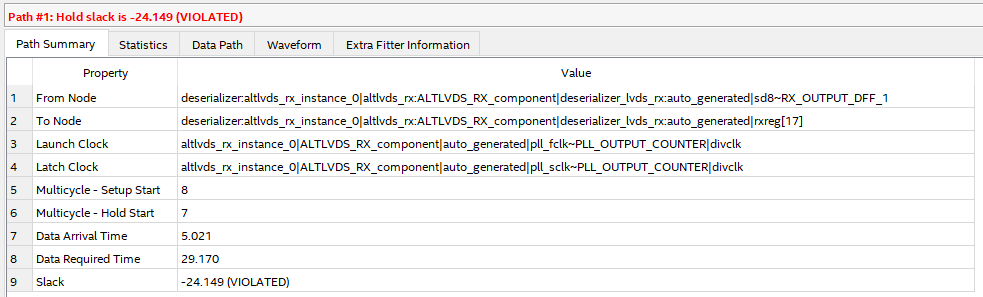

The timing analysis shows no problems with 400 MHz input clock, but shows huge hold time violations when using 300 MHz input clock. We were able to replicate this behavior with a completely empty project which only contains a single ALTLVDS_RX.

I have attached this simple project. Compiling the design with Quartus Prime 18.0.0 Build 614 04/24/2018 SJ Standard Edition will result in huge hold time violations within ALTLVDS_RX.

You can modify the design for 400 MHz

* Reconfigure ALTLVDS_RX with 800 Mbps input data rate and 400 MHz input clock rate

* Change clock period in SDC file to 2.000 ns

Can someone explain the hold time violations with 300 MHz input clock?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

My name is Hazlina and I am the senior manager of the applications engineering team supporting this forum. I apologize for the delay in responding to your inquiry. Please note that most of the engineers are still out on Chinese New Year vacation. They will be back next week and will take a look at this post first thing next week.

Again, I apologize for the delay.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Simon,

I just back from Chinese New year,

I had look into your design, firstly, your design are just LVDS without any other logic. The constrain might be inappropriate.

Secondly, you can look into https://www.intel.com/content/altera-www/global/en_us/index/support/support-resources/knowledge-base/solutions/rd10232012_61.html

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kenny

note that in our "real" design the ALTLVDS_RX is actually driving logic. We are seeing the same hold-time violations as are visible in the empty example project. I attached this empty example project to provide an easily reproducible test case. Please let us know which timing constraints we should use if you still think that the constraints "might not be appropriate".

I had a look at the link you provided. Please note that we are seeing hold-time violations. The document you provide seems to discuss the case of setup-time violations, i.e. if the input clock rate is too fast too fast for the design/FPGA. The document does not talk about hold time violations.

Again, the problem is that we are seeing hold-time violations at 300 MHz which do not appear when constraining for 200 MHz or 400 MHz input clock rate. We need your support to understand why these hold-time violations occur and how to fix them.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You may refer to https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_altlvds.pdf page 44 on how to constrain the LVDS design. Once you have follow, you may reattached the design for me to make analysis again.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We have added input delay constraints as suggested in the user guide. The constraints are based around a 300 MHz DDR interface where the data and clock are center aligned.

Note that hold time violations are still present.

Please note that hold time violations are within ALTLVDS_RX IP.

We have also found that the hold time violations disappear if we modify constraints for 333 MHz clock instead of 300 MHz (see altlvds_rx_333.sdc).

Maybe there is a problem with specifying fractional clock periods?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I manage to duplicate the violation, I am still looking into it since the violation happened inside the LVDS.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have implemented these changes in our "real" design and can confirm that the fitter no longer hangs and the hold time violation is no longer present.

Is this setting in the quartus.ini file recommended to be used as default? Or is there some drawback to use it?

Thanks for your support.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Should be no drawback, usually quartus.ini used to handled certain problem. You do not need to use it as default.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page