- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi expert,

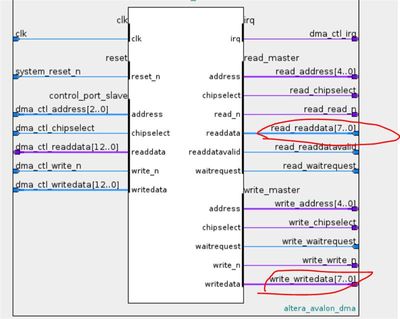

I want to change the data width of read master and write master, but it seems there is no way to change it. Do you know how to change that?

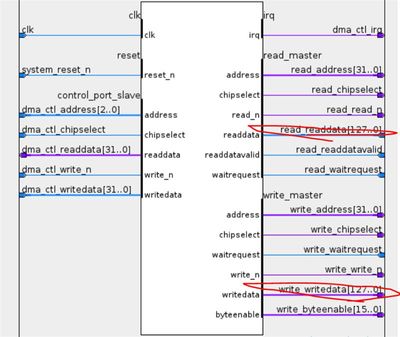

Long time ago, I successfully changed it to 128bit and there is also a byte enable signal in write port.

Thanks!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You probably just need to change a parameter. Reopen the parameter editor for the IP (may be a .qsys or .ip file depending on if you're using Standard or Pro) and change the parameter. Most IP like this and their parameters are documented here: https://www.intel.com/content/www/us/en/docs/programmable/683130/22-3.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

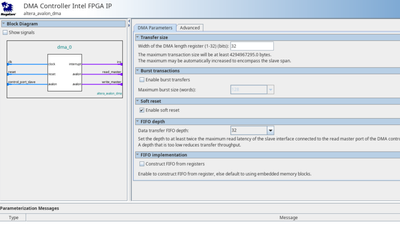

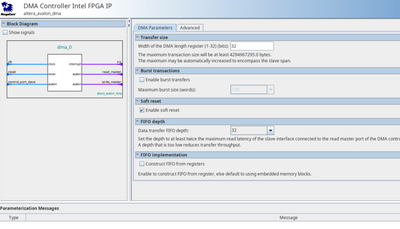

But there nowhere to change it in parameter editor:

BTW, I am not using blackbox.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

But there nowhere to change it in parameter editor:

BTW, I am not using blackbox.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

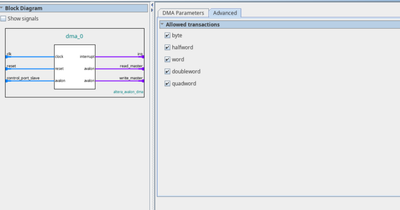

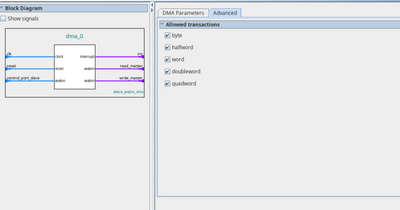

go through this document. if you see here quadword support 128 bit.

may i know which version did you used previously?

Thanks,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can see my snapshot, I have already enabled quadword, but readdata is still 8 bit.

I am using Quartus 21.3 and 21.4.

BTW, you can check the "show signals" box in your picture to see the signal width. Is it a 128bit width?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

- Byte (8-bit), halfword (16-bit), word (32-bit), doubleword (64-bit) or quadword (128-bit)

those are transfer type, there is no option to change width.

i want to know on which version you did those changes?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I used to use 21.3 to generate 128width.

"there is no option to change width" ---- I think it is not reasonable since the performance is too much low with 8 bit width.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello,

I have replied your email for arranging a call, but I don't see feedback. Can you ping me directly? Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Small doubt, in you previous DMA (128 bit support IP) can able to trans for 128 bits, because this ip design can support only 8 bit's only. did checked that?

Thank you,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes. It can transfer 128bits and worked perfectly well. I have also tested it on FPGA board.

You can double check with the IP I sent to you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

please follow bellow article may be it helps you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

i discoursed with engineering team every one, telling we don't have option to vary the data width of DMA. i shared your platform design also, they telling you did changes in source code. Actually we are not able to give support for source code changing. if any problem is there in working of IP we can give support. sorry.

in DMA controller IP document you see functionality of DMA

https://www.intel.com/content/www/us/en/docs/programmable/683130/22-3/dma-parameters-basic.html

Thank you,

Hareesh B.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As we do not receive any response from you on the previous question/reply/answer that we have provided. Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page