- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In my design, I have a 6b x 12b multiplier that is inferred from code that is essentially if(rising_edge(clock)) then

if (clock_enable = '1') then

result <= num_6b * num_12b;

end if;

end if;

The design compiles fine, simulates fine, and runs fine, but the compiler throws the warning:

Warning (222013): Relative toggle rates could not be calculated because no clock domain could be identified for some nodes

And my power analysis report gives the low confidence metric. I also have a specified POWER_DEFAULT_TOGGLE_RATE set for the design, so I'm not sure why the tool is unable to determine the clock domain or use the default toggle rate. Is this a bug in the tool? Is there some other work around for me to tell it explicitly the toggle rate for this particular multiply operation? My clock is 30MHz and my clock enable is 5KHz.

Thanks!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Did you properly set up a .sdc file with clock constraints defining this information? And did you enable the vectorless estimation option in the Power Analyzer?

Using the default toggle rate will always give you the low confidence metric. You need to supply more detailed info, such as a .vcd file from a simulation or manually create Power Toggle Rate or Power Toggle Rate Percentage assignments.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The design is fully constrained and the clock is defined per the sdc. The design also has thousands of other nets that the tool associates with a clock domain, and it is using my I/O and default toggle rates (percentages I input into the tool) without any problem on those thousands of other nets.

I am trying to find out why in particular it cannot associate a clock domain automatically with those 18 nets after it infers the multiplier from my VHDL. This is a deep dive question as to why those 18 nets are behaving differently from the thousands of other nets in the design where the power analysis tool finds the clock domain without any issue. I know that it is the 18 nets of the multiplier because in the power analysis report, they are listed under "indeterminate toggle rates."

Even if my default toggle rates cause the tool to give a low confidence rating versus a vcd, I should still be able to get an answer to this question from someone in the factory who understands why the multiplier IP in the Max 10 is causing the power analysis tool to treat the registered multiply as if it is unregistered?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Susan,

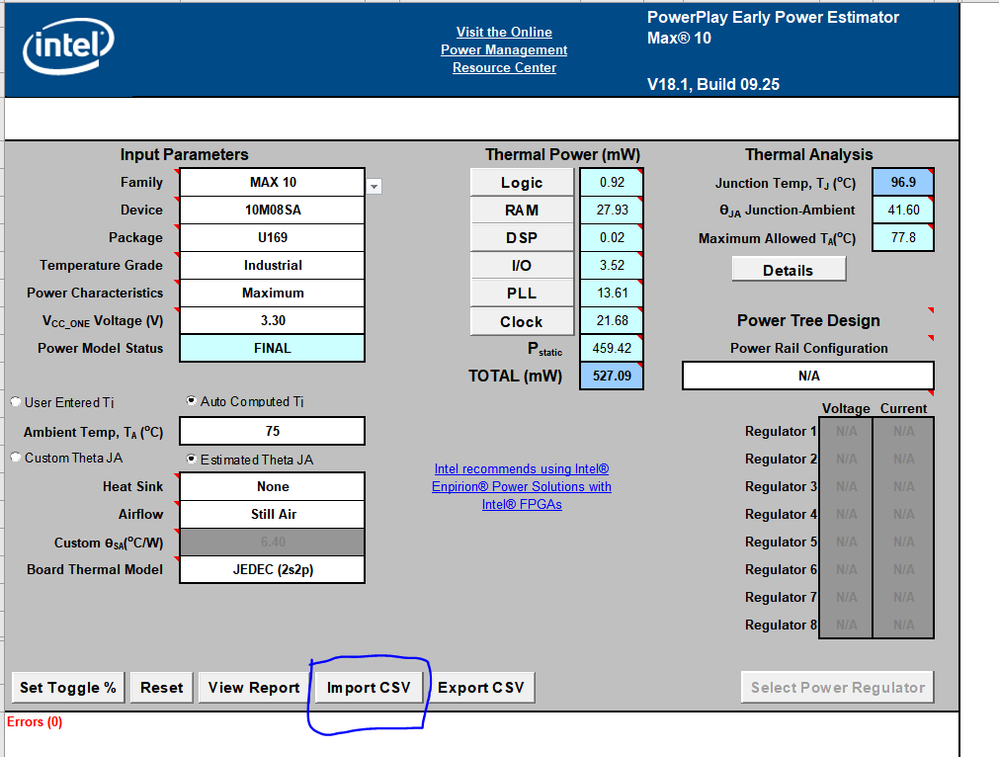

Can you attach your EPE ? we can take a look.

Another thing is did you load .csv into EPE or just manually update the parameters into EPE?

regards,

Farabi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Farabi, I am attaching the csv from Early Power Estimator. I don't see a place in the tool for me to load a .csv as input to EPE. My choices are to input a VCD or to specify the default toggle rate, which is what I did. I do notice in the EPE it does recognize the 18b multiply and that the output is registered. It shows no register on the input (the data is registered elsewhere prior to the multiply) or pipeline register, so maybe that is what is causing the zero toggle rate to be assumed? I can experiment by turning on extra registers in the multiplier to see if that fixes the power estimate, but since the design easily meets timing, I don't want to add two pipeline delays permanently to the design.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Susan,

I load your .csv file into MAX10 EPE and the power estimator calculates the power estimation correctly.

To download MAX10 EPE : https://www.intel.com/content/www/us/en/support/programmable/support-resources/power/mxv-power-est-download.html

I attached the EPE for your convenience.

Open the EPE , then load csv file like below pic:

The calculation will executed right after you load the .csv file into EPE. Then go to report tab to see the result.

regards,

Farabi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry - when I said I don't see a way to import csv to EPE, that wasn't what I meant. I have never had trouble with EPE. My problems are in the Quartus power analyzer, after the design has been synthesized, placed, and routed, not in the standalone EPE spreadsheet calculation. Does that provide any clues, the fact that it works fine in EPE and recognizes the multiplier's internal nodes with the proper toggle frequency but can't after synthesize/p&r in the Quartus tool? My design has to be analyzed by that tool, not EPE.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The way to get power estimates with high confidence is to use the toggle rate that comes from simulation or user-entered assignments. Refer to the "Confidence Metric Details" section in the link below,

https://www.intel.com/content/www/us/en/programmable/documentation/osq1513989409475.html

That being said, the way to tell the Power Analyzer Tool to use toggle rate from the simulation is with a vcd file. Here is a small guide to generate a vcd file in ModelSim,

https://www.intel.com/content/www/us/en/programmable/support/support-resources/knowledge-base/solutions/rd07062010_692.html

regards,

Farabi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We do not receive any response from you to the previous question/reply/answer that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

regards,

Farabi

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page