- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

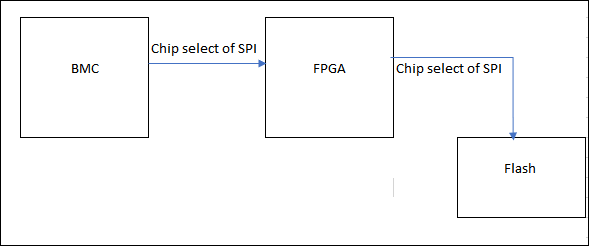

We are using MAX 10 FPGA "10M40DAF484C7G" device in our project. Chip select for the Board management controller(AST 2600) is routed through this device which connects to the flash. As a result BMC is getting corrupted most of the times during FPGA programming. We have tried ISP clamp feature to avoid the corruption and the below is our observations.

- Programming is taking very long time.

- We tried by assigning CS which is output of FPGA value as "low" in .ips file. We have seen that once the programming is initiated CS is driven low.

- Even after using the ISP clamp feature we still see the BMC corruption.

We would like to know if there is any way to drive the CS low only during the CFM is loaded to SRAM, Not once the programming is initiated. And is there any other feature which we can use to avoid this corruption.

Any suggestions are much appreciated

Thanks and Regards

Naveen

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello NKuma10,

Thank you for posting your question on this Intel® Community.

We have a forum for specific issues about Intel® FPGA. For this reason, we are moving this thread to the Programmable Devices forum.

Wanner G.

Intel Server Specialist

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just to clarify, what is a CS pin on MAX10?

Thank You

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi YuanLi,

Chip select(CS) of Board management controller to access its flash memory through SPI interface is an output pin of the MAX10 FPGA.

Regards

Naveen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI NKuma10,

I believe that the "CS" pin that is used to connect to the FLASH is actually a GPIO on MAX 10. So your concern is how to make it low during programming and in user mode?

Thank You.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page