- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

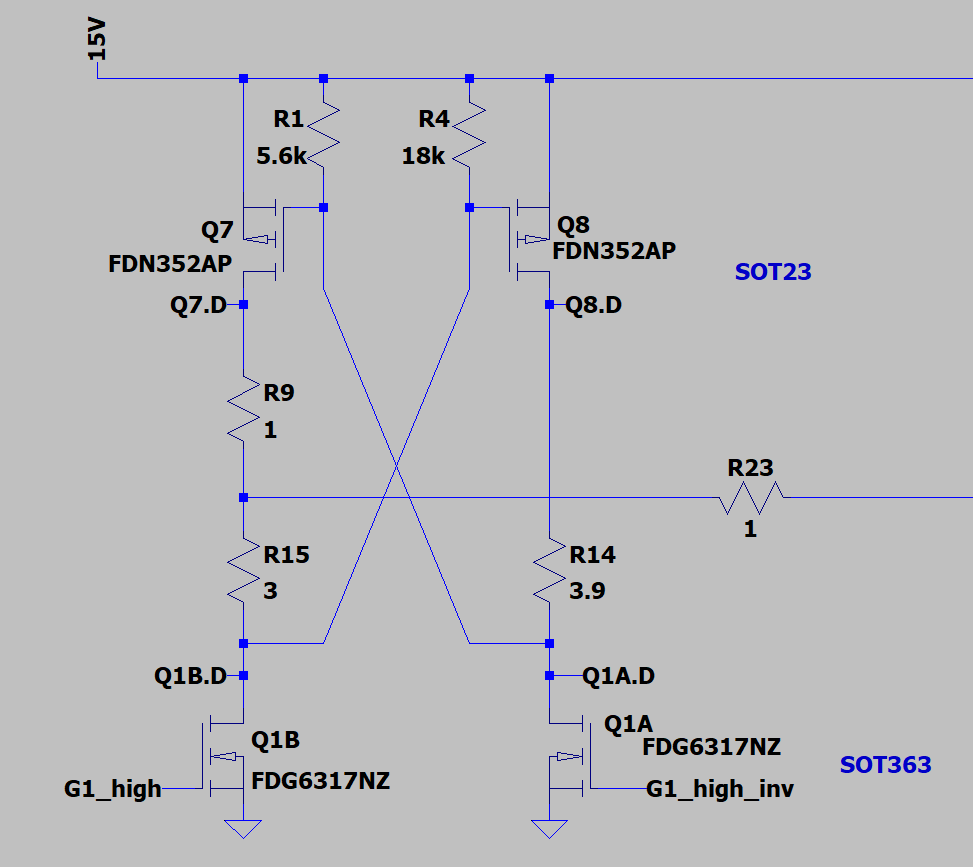

I am working on a gate driver design using the Intel MAX 10 10M08SAU169I7G. The FPGA is driving the signals G1_high and G1_high_inv in the attached schematic. The supply rail available (so far) is 3.3V. At this voltage I can select drive strengths 2mA for LVCMOS and 8mA for LVTTL. If I reduce the voltage to 3.0V, I can select drive strength 16mA for both LVCMOS and LVTTL. I have been able to translate the IBIS models to spice.

Results:

- CMOS is faster than LVTTL at the same voltage(3.0V) + drive strength (16mA).

- 16mA is faster than 8mA at the same voltage (3.0V)

Questions:

- Can I safely configure the outputs as 3.0V LVCMOS 16mA outputs with VCC=3.3V if this gives me the best results in my circuit?

- If this is not safe, what would go wrong? The toggle rate is low (1.5kHz) so there will be no problem with heat.

- I assume that the limitation in drive strength for the IO standards is due to the fact that the output pin will not be able to drive the output at the wanted drive strength and meet the IO standard requirements (VCC-0.2V for LVCMOS). Please elaborate?

- Is there any real difference in the IO buffer between LVCMOS and LVTTL for the same voltage + drive strengths?

- What would be my best option in your opinion to speed up this gate driver stage?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I apologize for the late reply. Here's my response to your questions:

a. Can I safely configure the outputs as 3.0V LVCMOS 16mA outputs with VCC=3.3V if this gives me the best results in my circuit?

No. You can only set it as 3.0 V with 30V LVCMOS. Please refer to table 4 from page 9 of this document https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/ug_m10_gpio.pdf

b. If this is not safe, what would go wrong? The toggle rate is low (1.5kHz) so there will be no problem with heat.

Unfortunately we do not have that information out of our specifications from the document.

c. I assume that the limitation in drive strength for the IO standards is due to the fact that the output pin will not be able to drive the output at the wanted drive strength and meet the IO standard requirements (VCC-0.2V for LVCMOS). Please elaborate?

Can you explain more about this question for me?

d. Is there any real difference in the IO buffer between LVCMOS and LVTTL for the same voltage + drive strengths?

These IO buffers are similar based on the document I provided.

e. What would be my best option in your opinion to speed up this gate driver stage?

That will depend on your signal integrity and your design.

Hope this helps. Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

a. Can I safely configure the outputs as 3.0V LVCMOS 16mA outputs with VCC=3.3V if this gives me the best results in my circuit?

No. You can only set it as 3.0 V with 30V LVCMOS. Please refer to table 4 from page 9 of this document https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/ug_m10_gpio.pdf

I have read the documentation. I see that there is no option to have 16mA drive strength at 3.3V. The problem is that I do not understand why.

b. If this is not safe, what would go wrong? The toggle rate is low (1.5kHz) so there will be no problem with heat.

Unfortunately we do not have that information out of our specifications from the document.

c. I assume that the limitation in drive strength for the IO standards is due to the fact that the output pin will not be able to drive the output at the wanted drive strength and meet the IO standard requirements (VCC-0.2V for LVCMOS). Please elaborate?

Can you explain more about this question for me?

VOH (high level output voltage) is specified as VCC-0.2V (min) for LVCMOS. The output buffer is not able to fulfil this at 16mA drive strength with a supply voltage of 3.3V. I understand this. I am not interfacing to an LVCMOS device but a pair of mosfets with a threshold voltage of 1.5V(max). I wonder if the limited choices for drive strength at VCC=3.3V has to do with which logic standards can be met more than which drive strengths (output impedance) can be set with no damage to the device?

d. Is there any real difference in the IO buffer between LVCMOS and LVTTL for the same voltage + drive strengths?

These IO buffers are similar based on the document I provided.

Yes, I can see that from the tables. I still wonder if there is any real difference at the silicon level.

e. What would be my best option in your opinion to speed up this gate driver stage?

That will depend on your signal integrity and your design.

To be clear: To be able to drive the mosfets fast, I need low output impedance. The MAX10 device I use needs 3.3V to work, so I have this supply rail in the design. It seems that I would need to generate another supply rail at 3.0V to be able to set the output buffers at full (16mA) drive strength. This seems strange. I do not understand how setting full(16mA) drive strength at 3.3V could damage the output buffer assuming that I keep the switching frequency and thereby losses low.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I like your enthusiasm on trying to learn our FPGAs in deeper level. However, I am not able to validate any settings beyond our specification from our documents. I would advise you not to do it since I cannot guarantee that it will be safe for your device but it will be up to you to experiment that.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I hope that answers your question. I will close this case in 3 days if there is no further question from you.

Thanks

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page