- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello not sure to place question here or on Quartus.

I got back and try'd again latest release, so a great doubt it is time to retirement?

[noob mode on]

How to evaluate these small vhdl snippet, what wrong on?

version 2

AvaT80_Wait_n <= '1' when Wait_n ='1' and -- Z80 external wait active low

IRQ_waitrequest ='0' and io_waitrequest = '0' and mem_waitrequest ='0' else '0'; -- Avalon channel Wait too

version 1

AvaT80_Wait_n <= Wait_n and -- Z80 external wait active low

not(IRQ_waitrequest or io_waitrequest or mem_waitrequest); -- Avalon channel Wait too

A <= A_Bus;

MC <= AvaT80_Wait_n & std_logic_vector(MCycle);

TS <= Local_Z80clk & std_logic_vector(TState);

DEBUG_STAT(3 downto 0) <= not Wait_n & IRQ_waitrequest & io_waitrequest & mem_waitrequest;

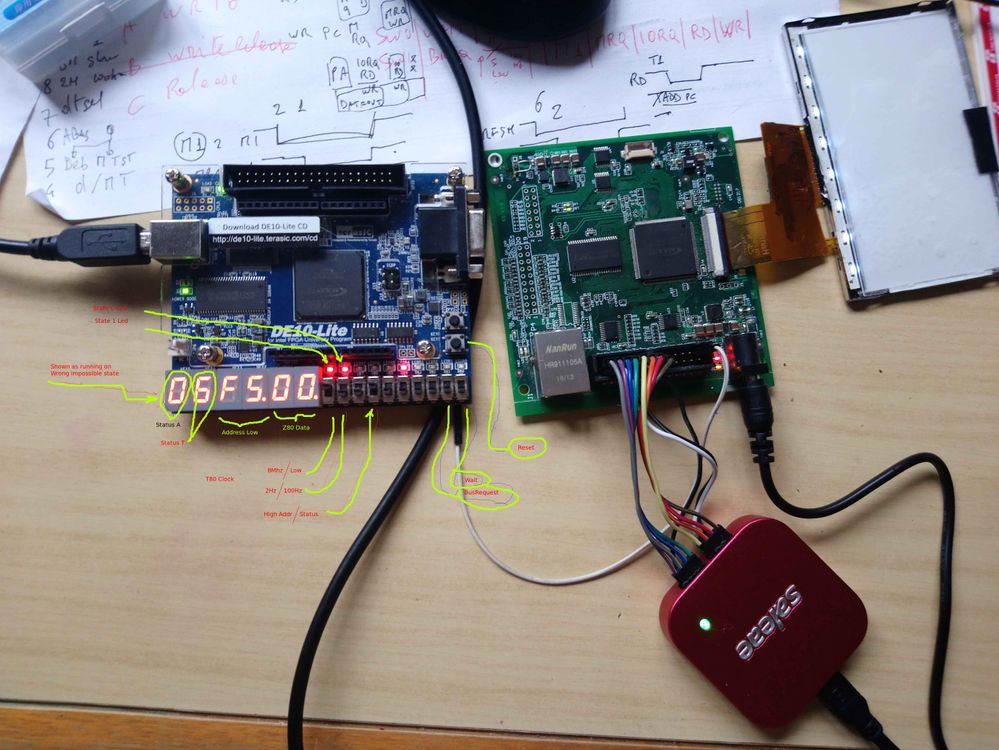

this snippet is part of T80 interface to Avalon, this way can be used on QSYS fabric.

this is at top level driving board Led

Local_AvST1 <= '1' when Local_Debug_Port(7 downto 4)= "0001" else '0';

Local_AvSTC <= '1' when Local_Debug_Port(7 downto 4)= "1100" else '0';

Local_Debug_Port(7 downto 4) is attached to leftmost display on DE10Lite, Local_AvSTx to Led9, 8.

Tryd on custom board too, routed signals to Salea, here what i see

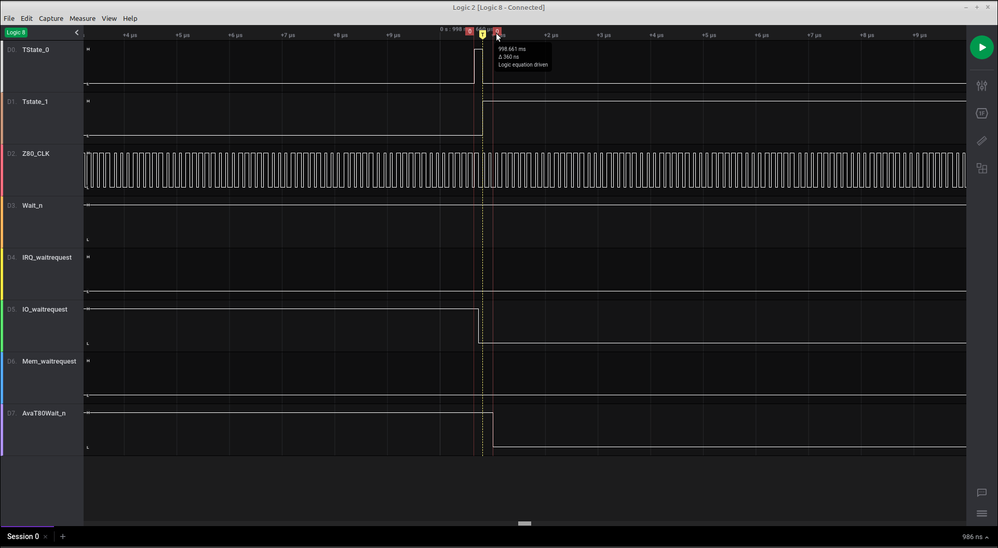

Both version of snippet as seen on LA

Forcing equation to '1' result in this:

AvaT80_Wait_n <= '1;

it resemble tstate_0 xor tstate_1 but equation say assigned stuck at one.

I appreciate help also if tell me to go back learning unknown trick.

[noobs mode off]

I have no idea about if it is software or hardware related or why not combined.

Thank all try help on.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

There are some missing files in the ZIP file.

Warning (12019): Can't analyze file -- file Z80test_LCD_NoNios_Debug/synthesis/Z80test_LCD_NoNios_Debug.vhd is missing

Warning (12019): Can't analyze file -- file ../../my_Core/Protti_PP52/Z80_ROM_MMU_ver1_02.vhd is missing

Warning (12019): Can't analyze file -- file ../../my_Core/T80/T80avalon_006.vhd is missing

Could you provide the design QAR file by clicking on Project > Archive Project > Archive

Thanks

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I can send in NDA form, this way cannot publish here.

Custom board is SRAM based, LCD IPCORE fail an odd way. Ethernet added to inspect, core failed too on combinatorial terms. This scared me a lot about possible pattern sensitivity or software degrade.

Test (2018) was to add T80 core and see if LCD work. Some core got imported from Xilinx part or GAL where they run fine.

Suspended development for a long while....

Seen version 2020, last try was on Lite-10 board, LCD must be wired up to. After no success on I am porting to Xilinx Spartan-6 board to see what happen.

Max10 family appeared as best fit and secure way but Altera was no more Altera.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You may contact your local sales or distributor https://www.intel.com/content/www/us/en/partner/where-to-buy/overview.html.

Thanks

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I bought too many MAX10 part and board. I don't need manufacture more board costed a fortune and time none never pay for.

If you send me a private address I can send DE10-lite hosted design.

Plot of issue is present on files in zip, T80 Avalon has a MOORE automata clocked to 100MHz Avalon, cannot stay in initial state, must evolve to idle adsorbing or waiting on T2, so issue is unclear to me...

Again Wait state both used to T80 core (Free IP core), on LA mapping appear polarity reversed.

When wait signal driven to '1' what is on output? Why output appear so weird than '1' as expected to be?

No I don't buy nothing more.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have sent an email to you and we shall continue the discussion there.

Thanks

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have not heard from you since my last email. May I know if you have any update?

Thanks

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We do not receive any response from you to the previous question/reply/answer that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, I am completing port to Xilinx Spartan, to do so I teared down all QSYS logic and rewrote some part of IP core.

It is no more using Avalon is not supported on, use instead native block, it seems not suffering none of issue experienced. The one are here are justified I don't know about, Its since long long time I migrated to Altera, Xilinx and Lattice too changed a lot and actual family are new to me.

I am rewriting IP as platform/vendor neutral to isolate issue. Actual issue are not similar to what I encountered on MAX10, just fresh code is not as clean as the old one used for years no more Avalon/Qsys oriented.

Think it took few day more to complete.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Status Update:

Porting to Spartan 6 complete.

During port I observed QSYS generate a lot of polarity invert to same signals, inserted a lot of adapter too. No idea why spreading invert across nested modules nor what is inside due it is scrambled preventing dissection.

Removed all interconnection from QSYS, so now Avalon bus is just driven by a simulated one: simple 6 way address and data multiplexer. Arbitration is driven by a simple round robin 2 queue VHDL ONLY state machine. This same deterministic SM is tight coupled to multiplexer.

No issue were present, wait status is clean, all other signals clean also without constraint. Logic was pipelined a lot on before port in the far past. High speed part IP Core locking or behaving weird on MAX 10 run fine on Spartan 6 tested @300MHz.

T80 boot up then stop on code protection but has it reason on limited RAM resources of model used. Next Xilinx step is to get a board with on board ram to assign full resources than minimal permitted by block ram.

T80 on Altera appeared to run fine when wait fixed to 1 but LCD Ip core locked and scrambled on Ram access. T80 was ok accessing ram. This can infer possible doubt about SVerilog fabric or mixed language issue. QSYS forever add SVerilog modules. Scrambled source limit further test on my side.

Future evaluation can be done on Lattice ICE40 part too, MAX10 raised too much pricing.

Next step to isolate issue is to port back this new design to Altera board and test again leaving Verilog and QSYS free. Too much time and effort was on board manufacture and test. Ready to sell since y17 never useable after first prototype from version 15.x and ES part.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sure. Thanks for the update. Do let me know if you have any questions.

Thanks

Best regards,

KhaiY

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page