- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there,

I am using Intel Agilex-F series development which uses P-tile. I am trying to enable P-tile Debug took kit on the Intel reference design. I am referring to Section 7.2 of P-tile Debug tool kit.

What I want to clarify is if I want o just view the P-tile status information and not configure anything to the registers, is it as simple as below steps:

1. Enable Debug Tool kit in Pcie IP configuration

2. Connect a clock to the xcvr_reconfig_clk port of the instantiation

3. Add a pin constraint to connect the xcvr_reconfig_clk to a 100 MHz clock source.

My question is do I need to drive any other signals on the xcvr_reconfig* interface to observe the DebugTool kit?

Thanks

Binu

- Tags:

- p-tile

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Binu,

If the Debug Toolkit and the Hard IP Reconfiguration interface are enabled in the dynamically-generated design example, please check that the hip_reconfig_clk clock is connected to its respective clock source and the pin assignment is made properly.

For further information, you may refer to link below, Section 7.2.1. Overview, https://www.intel.com/content/www/us/en/docs/programmable/683059/23-4-9-1-0/overview-85177.html

Best regards,

zying

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zying,

Thank you for your reply.

I am aware about the Section 7.2.1 and as mentioned in my original question connecting the clock source and pin assignment is clear to me. But what is unclear is if that is all is needed or do I need to drive any other signals on the xcvr_reconfig* interface to observe the DebugTool kit?

Can you check with internal design team to clarify this? The document is inconclusive on this information.

Thanks

Binu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zying,

Following up on the above question. Any update?

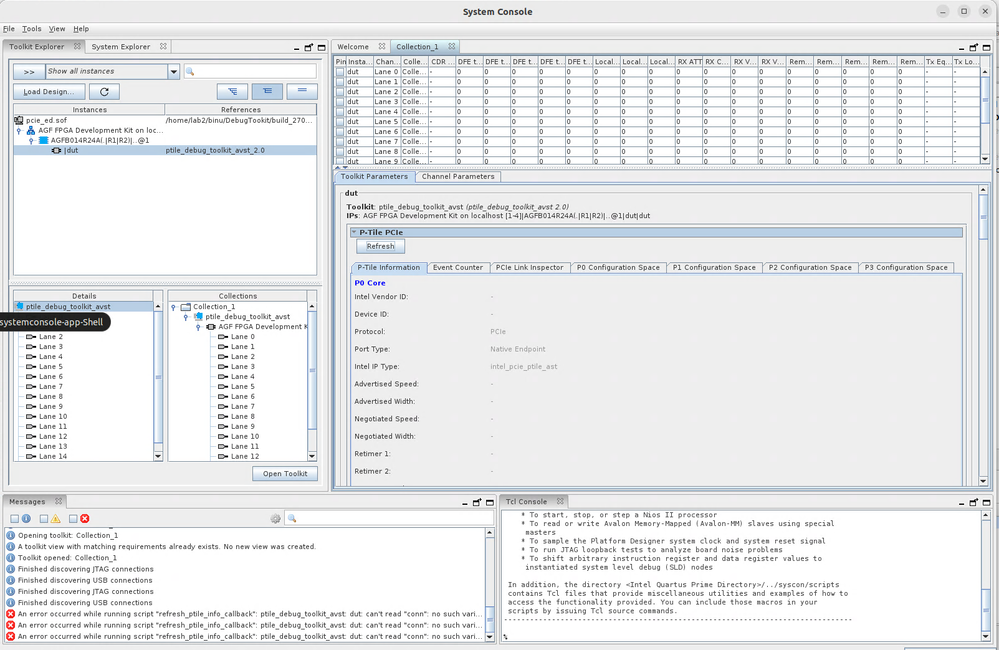

I got the DebugTool kit with the above changes/as mentioned in P-tile Debug tool kit using Quartus 23.4. But I get some errors on the System Controller interface. Screenshot below for reference.

Any input on this is much appreciated!

Thanks

Binu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you share your .qar file?

Best regards,

zying

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zying,

Please find attached the .qar file.

Thanks

Binu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Binu,

Can you share the .qar file again? The .qar file that you shared was corrupted because it was compilation unsuccessfully from my side.

Best regards,

zying

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zying,

My apologies. I have recompiled the design and regenerated qar file. Attaching here.

Thanks

Binu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Binu,

- Please make sure that you have turn on Enable PHY reconfiguration on the Top-Level Settings tab if you are using xcvr_reconfig. For further information, you may refer link below, Section 4.13. PHY Reconfiguration Interface, 4.13. PHY Reconfiguration Interface (intel.com)

- Please make sure that you have do the pin assignment and please connect all needed. You may refer to the example design under https://cdrdv2.intel.com/v1/dl/getContent/736492 . For further information, you may refer to our page, installer package, https://www.intel.com/content/www/us/en/products/details/fpga/development-kits/agilex/agf014.html

- For the PCIe, did you connect to the host ? are you reboot the host after programming the .sof ?

Best regards,

zying

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Binu,

Is there any update?

Best regards,

Zying

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zying,

No update. Unfortunately your previous response has nothing useful to my original questions. Have you or your design team had a chance to review the provided Quartus archive files?

Below is response to your questions:

- Please make sure that you have turn on Enable PHY reconfiguration on the Top-Level Settings tab if you are using xcvr_reconfig. For further information, you may refer link below, Section 4.13. PHY Reconfiguration Interface, 4.13. PHY Reconfiguration Interface (intel.com).

- [Binu] So enabling P-tile Debug tool kit is not enough? This goes back to my original question.

- Please make sure that you have do the pin assignment and please connect all needed. You may refer to the example design under https://cdrdv2.intel.com/v1/dl/getContent/736492 . For further information, you may refer to our page, installer package, https://www.intel.com/content/www/us/en/products/details/fpga/development-kits/agilex/agf014.html

- [Binu] As mentioned previously in this thread, I have made the clock pin assignment as mentioned in the guide. I am aware of Intel example design and that is the one I updated to enable Debug tool kit. So I am fully aware of the above links and have mentioned my steps clearly. Providing the links again and again is not helpful.

- For the PCIe, did you connect to the host ? are you reboot the host after programming the .sof ?

- [Binu] Yes of course connected to host for checking PCIe link status.

From what you are saying, I don't think you have a solution for my question. That is unless you can clarify with your internal design team.

Regards

Binu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Binu,

I have sent the meeting invitation to your email. Please do let me know if you haven't receive it.

Best regards,

Zi Ying

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Binu,

Since you are not joining, so I will create a new meeting on tomorrow which is 1pm GMT +8 time zone.

Beside that, please do provide me your proper email and I will sent my invitation to that email.

Best regards,

Zying

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zying,

Unfortunately your email came through closer to meeting time which didn't help.

I have sent you my work email on a separate email to you.

Regards

Binu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Binu,

I have sent the meeting invitation to your work email. Please do let me know if you haven't receive it.

Best regards,

zying

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zying,

I have accepted your meeting invitation. Talk to you then.

I would like to provide additional information prior to meeting.

- Screenshot of System console/Debug tool kit interface showing no link layer information populated eventhough design is loaded. This was previously provided in this thread. But attaching again.

- Below is text of error message:

ptile_debug_toolkit_avst: dut

SEVERE: An error occurred while running script "refresh_ptile_info_callback

": ptile_debug_toolkit_avst: dut: can't read "conn": no such variable

while executing

"puts -nonewline $conn $json_cmd_msg"

(procedure "ptile_pcie_pysv_pkg::send_msg" line 5)

invoked from within

"ptile_pcie_pysv_pkg::send_msg $opDict"

(procedure "read_reg" line 3)

invoked from within

"read_reg "${pcie_path}.device_id_vendor_id_reg.pci_type0_vendor_id""

(procedure "ptile_pcie_driver_pkg::get_ptile_info" line 5)

invoked from within

"ptile_pcie_driver_pkg::get_ptile_info $i"

(procedure "refresh_ptile_info_callback" line 12)

invoked from within

"refresh_ptile_info_callback"

Thanks

Binu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Binu,

Could you share your .qar file?

Best regards,

zying

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Binu,

Initial comment of the error message from the team :

The “Conn” is a local connection which created to connect the python backend script to proceed the register read/write operation.

Below issue suspect that the connection between frontend and backend is not successful

Did you check back whether got any issue with the setup?

Best regards,

zying

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Binu,

Glad to hear that you resolved the issue by given suggestion below.

If you feel your support experience was less than a 9 or 10,

please allow me to correct it before closing or please let me know the cause so that I may improve your future support experience.

Regards,

ZiYing_Intel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page