- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

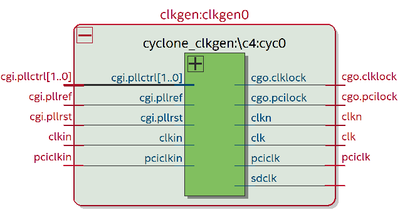

I'm mapping my VHDL design to Cyclone IV device. The SDRAM clock is derived from altpll's 2nd clock output. The compilation generates a warning message:

Warning (15899): PLL "clkgen:clkgen0|cyclone_clkgen:\c4:cyc0|cyclonepll:sdclkpll|altpll:\nosd:altpll0|altpll_3p21:auto_generated|pll1" has parameters clk1_multiply_by and clk1_divide_by specified but port CLK[1] is not connected

I check the design to make sure the CLK[1] is surely connected to the output by the following mapping:

And the output pin is connected to invalid

How could I fix this mapping problem?

Thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

To debug this, we need a sample case from you. Could you please send us the sample case so we can take a look into this?

regards,

Farabi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As we do not receive any response from you on the previous question/reply/answer that we have provided, please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page