- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I want to run my AFU in uClk_usr domain in the Streaming DMA AFU sample example. Please can you provide the steps that need to be followed in order to achieve this.

Thank you

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you

Navaneeth M

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know which acceleration card and software stack are you using?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Software stack - opae

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

If you are refering to https://www.intel.com/content/www/us/en/docs/programmable/683424/2-0-1/hardware-subsystems.html then the AFU is already connected to uClk.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are referring to the same document. But I'm afraid they're using pClk for the entire design.

Specifically, we wanted a guide or a series of steps which will help us in taking uClk_usr signal as an input signal in hw/rtl/QSYS_IPs/avst_decimator/avst_decimator.sv file. The uClk_usr signal is present as input in hw/rtl/ccip_std_afu.sv but we are finding it difficult in order to correctly take it as input in the avst_decimator.sv file.

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you confirm if the "afu.sv" is using afu_clk?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, "afu.sv" is using the afu_clk.

But, it would be great if the uClk_usr is made available in avst_decimator.sv file.

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Where can I get the avst_decimator.sv file? I am not able to see the file in the AFU design.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Path to avst_decimator.sv is:

<path to streaming_dma_afu folder>/hw/rtl/QSYS_IPs/avst_decimator/avst_decimator.sv

OR

$OPAE_PLATFORM_ROOT/hw/samples/streaming_dma_afu/hw/rtl/QSYS_IPs/avst_decimator/avst_decimator.sv

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know if you are using DCP 2.0.1? For this version, I do not see this IP

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am not sure about the DCP Version.

We are accessing the streaming dma afu folder by:

1. SSHing into devcloud

2. "devcloud_login" into "Stratix 10 PAC Compilation and Programming - RTL AFU, OpenCL" node

3. Performing "tools_setup" of "Stratix 10 PAC Compilation and Programming - RTL AFU, OpenCL"

4. cd "$OPAE_PLATFORM_ROOT/hw/samples/streaming_dma_afu"

The path to avst_decimator.sv is

"$OPAE_PLATFORM_ROOT/hw/samples/streaming_dma_afu/hw/rtl/QSYS_IPs/avst_decimator/avst_decimator.sv"

Expanded path is "/glob/development-tools/versions/fpgasupportstack/d5005/2.0.1/inteldevstack/d5005_ias_2_0_1_b237/hw/samples/streaming_dma_afu/hw/rtl/QSYS_IPs/avst_decimator/avst_decimator.sv"

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you try to download the official version and check if you can work with the latest AFU design?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Upon checking, the "avst_decimator.sv" file does not have user clock as input in this version as well.

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry, I was looking at the wrong directory. After looking at the correct directory then I am able to find the file.

You can modify the file in ccip_std_afu.sv so that the AFU IP is using UserClk and not Pclk.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

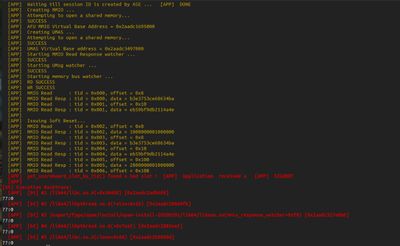

We tried using uClk_usr instead of pClk in line 117 of "ccip_std_afu.sv" file. We got the following error when we ran the software in simulation mode:

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

It looks like the PCIe IP is using PCLK and the AFU is running using uclk_user which is not able to match the frequency. You will need to implement clock crossing to make sure that the clock is able to pass to the AFU design without any issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you please list the steps in order to implement clock crossing.

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

After further checking, the rtl should not be change. You will need to modify the json file so that it is using uclk_usr. You may refer to "hello_mem_afu" example design json file.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you please tell us the location of the SDC file in the streaming dma afu folder?

Also, could you please tell us the additions that we have to make to the SDC file?

Thank you

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page