- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm using EPCQL512 with 10AX115N2F40 in a known good hardware design.

Quartus Prime 20.1.1

Quartus Programmer & USB Blaster

What works:

Creating a jic file encapsulating a factory SFL image works when programming the serial flash.

An Auto Detect after the factory SFL image is loaded shows the full chain with EPCQL512 attached to the A10 device.

What doesn't:

When I add an SFL instance (per AN-370 | 2019.02.18) to the top level of my design, compile and load my design sof, I don't see a serial flash device attached when auto detecting after loading. I see the SFL in the technology map viewer for the compiled design, so I know it should be there in the JTAG chain.

Are there device/pin options that must be configured correctly for this to work?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When comparing the behavior of the factory SFL image and my design with SFL IP added I still don't understand why the attached serial flash shows up in a JTAG scan with the factory image loaded, and not in a scan when my design is loaded.

However, after deciding to assume that the SFL in my design otherwise works and testing JTAG access to serial flash (such as doing a flash verification operation without having to first load the factory SFL image) the SFL IP does appear to bridge JTAG and ASMI.

I create and load a jic file as usual, then uncheck the box for configuring the factory SFL image prior to flash access. My design remains loaded in the FPGA, and I can verify or load the flash without disturbing FPGA operation.

So it works for my purposes, although with a minor quirk of not being able to detect the flash presence via a scan.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

SOF programming doesn't require SFL loader as it doesnt interact with the flash memory. Thus when you are attaching a SOF file, you dont see SFL loader there.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You miss the point of my complaint, which is not about the sof load, but what happens (or doesn't) after my design image is sof loaded into the device.

As I understand it, the intent of the SFL IP is to bridge JTAG to ASMI, just as is done in the factory SFL image typically used in jic programming of attached serial flash devices. After I do a typical flash programming operation, which loads the factory SFL image into the FPGA, I can observe the functionality of that bridge because an auto detect shows the attached flash device.

I am expecting the same behavior from my design when it contains SFL IP, and I don't see that.

My intent is to be able to access the flash via JTAG without having to load the factory SFL image.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

To access the flash via JTAG, you will need a controller in the FPGA which i will suggest the usage of SFL IP. Meaning to say, you need to have this IP in your SOF file. Unless, you have a direct connection from JTAG to FLASH without using FPGA. Otherwise, a controller is a must for that.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

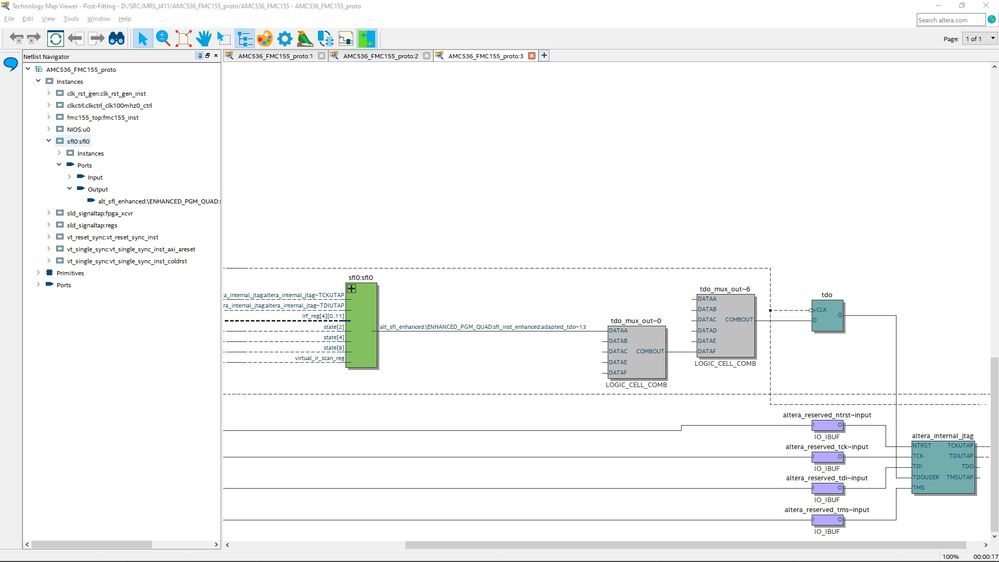

As I said in my first post, I have added the SFL IP to my design. Below is the SFL in the post fitting viewer. I still don't see the serial flash in a chain auto detect after loading this design.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Additional information: I do not have "Share ASMI interface with your design" checked. The only user port on the sfl is noe_in, which I have grounded and should enable operation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I think it is legit that SFL thing will not appear when SOF is attached. May i know what is your concern for not getting that SFL thing when putting SOF?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When comparing the behavior of the factory SFL image and my design with SFL IP added I still don't understand why the attached serial flash shows up in a JTAG scan with the factory image loaded, and not in a scan when my design is loaded.

However, after deciding to assume that the SFL in my design otherwise works and testing JTAG access to serial flash (such as doing a flash verification operation without having to first load the factory SFL image) the SFL IP does appear to bridge JTAG and ASMI.

I create and load a jic file as usual, then uncheck the box for configuring the factory SFL image prior to flash access. My design remains loaded in the FPGA, and I can verify or load the flash without disturbing FPGA operation.

So it works for my purposes, although with a minor quirk of not being able to detect the flash presence via a scan.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page