- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello! I am looking for help with a SERDES setup using Quartus. First a brief problem description and then I will provide more details below.

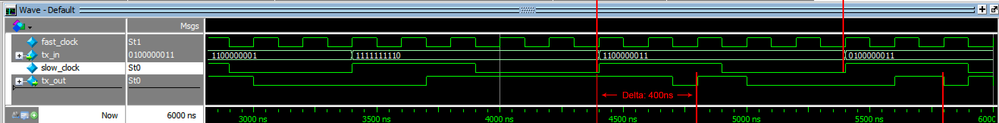

The 10-to-1 serializer is driven with two external clocks. I am feeding the input on the rising edge of the slow clock and 400ns later (in ModelSim at least) I get the serialized output out of Altera's Soft LVDS block. Each individual output state is aligned with the fast clock, but I do not see any output clock that I can use to tell the receiver when a new block of data begins. Where do I get a slow clock signal that's aligned with the SERDES output frame?

Boring details:

I am new to FPGAs and after completing a number of tutorials I found this nice HDMI one here:

https://www.fpga4fun.com/HDMI.html

As far as I can tell the signal generation for the three 10-bit channels is working fine, the last piece is getting those channels serialized and sent via the dedicated LVDS pins of the Altera MAX 10 that I am using.

I am using an ALTPLL block to create the basic signal clock C0 and a secondary C1 clock which is 5 times faster (according to Soft LVDS documentation). Each channel goes into an Altera LVDS instance (configured for external PLL) along with the two clock signals. Running the whole thing in ModelSim I see the expected data going in an coming out. The problem is, where can I grab a clock that is synchronized to the LVDS output? Can I rely on the simulation and add a 400ns delay or add another slow clock output with a 144 degree phase shift? Those ideas don't sound too great, so what is the recommended solution?

(Note: this is not the final clock speed, I am trying to slow things way below HDMI specs just so I can confirm waveforms on my slow oscilloscope)

Quartus project folder: https://www.dropbox.com/s/qdyt2bsp6rlotzh/hdmi-test.zip?dl=0

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sree,

Thank you for your response!

"isnt it slow clock is already aligned with your data ? I am not sure where iam missing out in your design."

The slow clock is correctly aligned with the incoming parallel data.

What I am looking for is some kind of framing signal for the outgoing serialized data (where does the 1st bit of the outgoing stream start?)

When using LVDS Serdes with its own internal PLL it generates an outgoing slow clock. When using LVDS Serdes with the external PLL I do not see any option to get an outgoing clock though

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page