- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello !

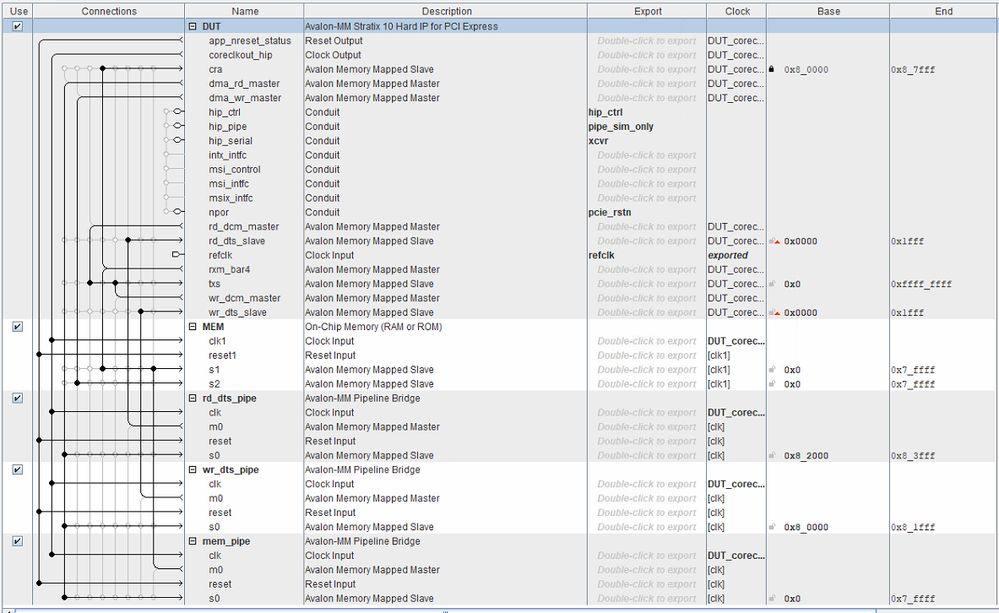

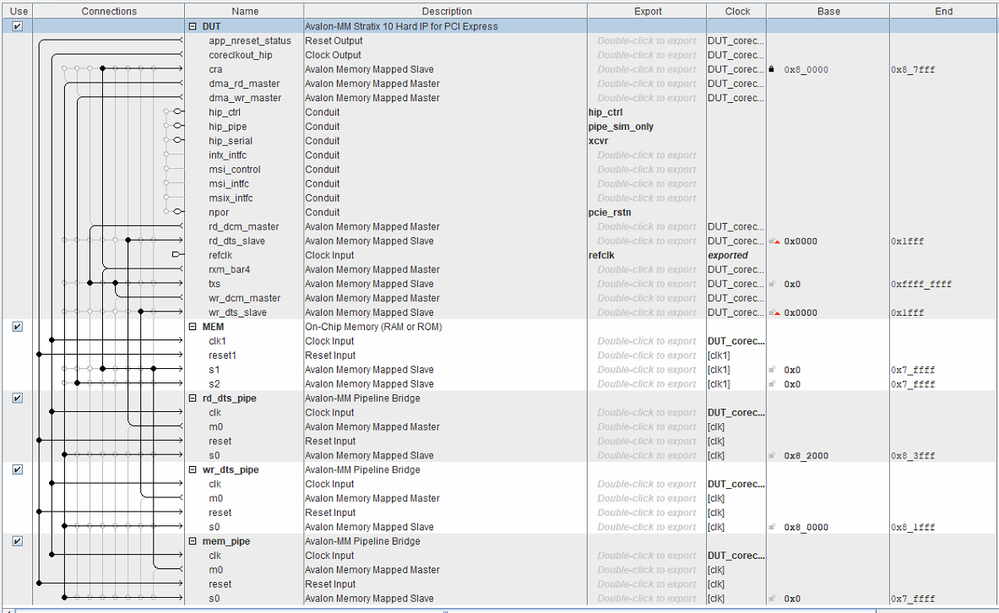

Working with a Stratix 10 board. Per AN 829: PCI Express* Avalon®-MM

DMA Reference Design built the design and uploaded it to the board. I work with Windows. I successfully run DMA Read, DMA Write. After the end of the DMA procedure, I register an MSI interrupt.

Than want to additionally register user interrupts. To do this, I use the intx_req_i input, which became available after selecting Export Interrupt conduit interface. And also tried using the rxm_irq_i[15..0] inputs. I apply a logical unit signal of a certain duration to these inputs, but I do not register an interrupt.

As I understood from the description, I must first enable interrupts by accessing the PCIe Interrupt Enable Register, which is located at 0x0050.

Please tell me how to properly translate the address from BAR in order to access this register from under windows. The map of connections and addresses is shown in the picture. Thank you. .

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for reaching, Apologize that I cannot get your question very clear.

- As I understood from the description, I must first enable interrupts by accessing the PCIe Interrupt Enable Register, which is located at 0x0050.

- Can I know which description and which document that you are referring at ?

- Please tell me how to properly translate the address from BAR in order to access this register from under windows.

- Can you specific which BAR that you need to translate ?

Also, I attach with AN 829 User guide, it might contain information that needed by you.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I wish to follow up with you about this forum case.

Hoping to hear back from you so that we can proceed for next step.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello ! thanks for your reply !

Your question :

- Can I know which description and which document that you are referring at ?

This is UG - 20033 (2019.07.18) Intel Stratix10 Avalon - MM Interface for PCI Express Solutions User Guide.

7.2.1. PCI Express Avalon-MM Bridge Register Address Map.

- Can you specific which BAR that you need to translate ?

as shown in the Qsys structure (picture above), from the BAR 0 register I get access to the DMA mechanism. bar4 provides access to the internal memory. at the moment I don’t know how to access the Avalon-MM to PCIe Interrupt Enable Register via CRA

thanks for the answer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For Avalon-MM to PCIe Interrupt Enable Register via CRA,

You may refer user guide at below link, there might got the information you needed.

Let me know if any other further clarification is needed.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your reply.

I have already seen this documentation many times. But I work with Stratix10 Avalon MM PCIExpress with DMA. I will repeat my question. It is as follows: how do I get access to these registers that you link to. Namely Avalon-MM to PCIe Interrupt Enable Register and Avalon-MM to PCIe Interrupt Status Register. Should it be a call through the BAR or is it a call to the configuration space type 0 , type 1 ?

thanks for your reply

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I dont understand your question on that, can you explain more where you stuck at ?

Are you mean you stuck on you not sure how to register Avalon-MM to PCIe Interrupt Enable Register?

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Good day! Thanks for your attempt to help.

Perhaps my first question was not read carefully.

Let's go first.

I am developing a system (PCIExpress endpoint) based on a Stratix 10 board. This card contains a PCI Express interface. To read and write data to the board, I independently develop a driver for the Windows operating system. I built the system using Quartus Platform Designer. System Contents is shown in the figure. With a driver and BAR0 register, I control reads and writes from the board via DMA. Also, if necessary, through BAR4 I carry out simple read and write operations in on-chip memory.

SYSTEM CONTENTS

When my algorithms work

I need to generate custom interrupts. For this I use the rxm_irq_i{15:0} interface. When a pulse is applied to any of these inputs, interrupt registration does not occur. From the descriptions of the AN 829 User guide and the Intel Stratix10 Avalon - MM Interface for PCI Express Solutions User Guide, I realized that I need to enable interrupts through the Avalon-MM to PCIe Interrupt Enable Register .

my question to you is how to access this register through driver in windows ? how to correctly translate the address in accordance with the system contents shown in the figure? or should I implement logic inside the FPGA? without the participation of the host, will provide access to this register through the CRA interface?

Thanks for your reply. I hope that this time you understand the question.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for clarifying the question.

my question to you is how to access this register through driver in windows ?

- I wish to help on that, but driver in window is out of my scope of support.

Because Intel does not support any driver issue. Perhaps I leave this to communities to answer.

how to correctly translate the address in accordance with the system contents shown in the figure?

- Can I know which address in the figure you wish to translate? based or end or others ?

or should I implement logic inside the FPGA? without the participation of the host, will provide access to this register through the CRA interface?

- Yes, you can try to implement it.

Also, if you are using rxm_irq_i signal, please noted that These signals are not available when the IP core is operating in DMA mode (i.e. when the Enable Avalon-MM DMA option in the Avalon-MM Settings tab of the GUI is set to On).

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I wish to follow up with you on this case.

Else, This thread will be transitioned to community support.

If you have a new question, feel free to open a new thread to get support from Intel experts.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ! Thanks for the answer.

You wrote:

……. if you are using rxm_irq_i signal, please noted that These signals are not available when the IP core is operating in DMA mode (i.e. when the Enable Avalon-MM DMA option in the Avalon-MM Settings tab of the GUI is set to On).

My question is in continuation of an open topic

How to generate a custom (MSI) interrupt with multiple sources? And when I need use Avalon-MM DMA?

In progect I will translate rxm_irq_i signals from altera_pcie_s10_hip_avmm_bridge.v module to top level ep_g3x8_avmmdma256_integrated.v.

When using .intx_req_i I only get the legacy interrupt, and DMA does not work because it will generate MSI interrupt.

I am currently using a design that I adapted for my board and that should be very familiar to your team:

Intel pcie example design.

https://community.intel.com/t5/FPGA-Wiki/Reference-Design-Gen3x8-AVMM-DMA-Stratix-10/ta-p/735907

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You can try to use AVMM code For Qsys-generated Avalon-MM PCIe Hard IP,

- it has up to 16 individual interrupt signals, RxmIrq_<n>[<m>:0], <m>< 16.

- All these inputs will be mapped to one single MSI interrupt output.

- You can create your logic to detect when the wireless frame is received,

- and then use the rxm_irq_i signal to trigger the interrupt. It should work.

- https://community.intel.com/t5/FPGA-Wiki/Handling-PCIe-Interrupts/ta-p/736044

For AVMM DMA,

- the DMA descriptor controller sends an MSI interrupt to the host via TXS interface.

- You need to enable export MSI interface to implement custom MSI interrupt handle

- and send the MSI interrupt via TXS interface,

- I apologize that there is no example for this as I can see.

- As far as I understand, you need to create a MSI (Memory Write) Transaction,

- and transmit it through the TXS interface based on the information that you obtain from the MSI conduit interface,

Hope this answer your question,

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ! Thanks.

In your last answer you wrote: You need to enable export MSI interface to implement custom MSI interrupt handle and send the MSI interrupt via TXS interface.....

I selected the option in platform designer – Export MSI/MSI-X conduit interface and after then, interface added to the top level of the project:

.intx_req_i (), // input, width = 1, intx_intfc.intx_req

.msi_intfc_o(), // output, width = 82, msi_intfc.msi_intfc

.msi_control_o(), // output, width = 16, msi_control.msi_control

.msix_intfc_o (), // output, width = 16, msix_intfc.msix_intfc

When trigger interrupt using input .intx_req_i (), OS (operating system) register legacy interrupt.

how this interface can help generate MSI interrupt ?

Can you give an example for your recommendations ? about which you wrote:

- ……….you need to create a MSI (Memory Write) Transaction,

- and transmit it through the TXS interface based on the information that you obtain from the MSI conduit interface,

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

To enable/generate MSI Interrupt. You can refer the link provided in the previous reply.

https://community.intel.com/t5/FPGA-Wiki/Handling-PCIe-Interrupts/ta-p/736044

If you have any doubt, you may refer to the design example , MSI Design Example for Stratix V

It might not exactly the same as Stratix 10. But you can refer to it as a case study.

Hope this is able to help.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

We do not receive any response from you.

This thread will be transitioned to community support.

If you have a new question, feel free to open a new thread to get support from Intel experts.

Otherwise, the community users will continue to help you on this thread. Thank you

If you feel your support experience was less than a 9 or 10,

please allow me to correct it before closing or please let me know the cause so that I may improve your future support experience.

Regards,

Wincent_Intel

__________________________________________________________________________________

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can this design be run on Stratix 10 AX board?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page