Hi,

Targeting to use Stratix 10 SX SoC FPGA for an application which includes transceiver working at ~22Gbps per channel. Such 4 to 8 lanes (both TX and Rx) may be there in use at a time. Initially thinking of using Stratix 10 SoC dev kit for Proof of concept. Here, my concern is the transceiver seed grades. I gone through the document and understood that the '1' is the fastest and 3 is the slowest in family. I understand the FPGA fabric speed grade, but unable to visualize the impact of Transceiver speed grade. Can anybody share more details on transceiver speed grades?

With Regards,

HPB

連結已複製

Hi,

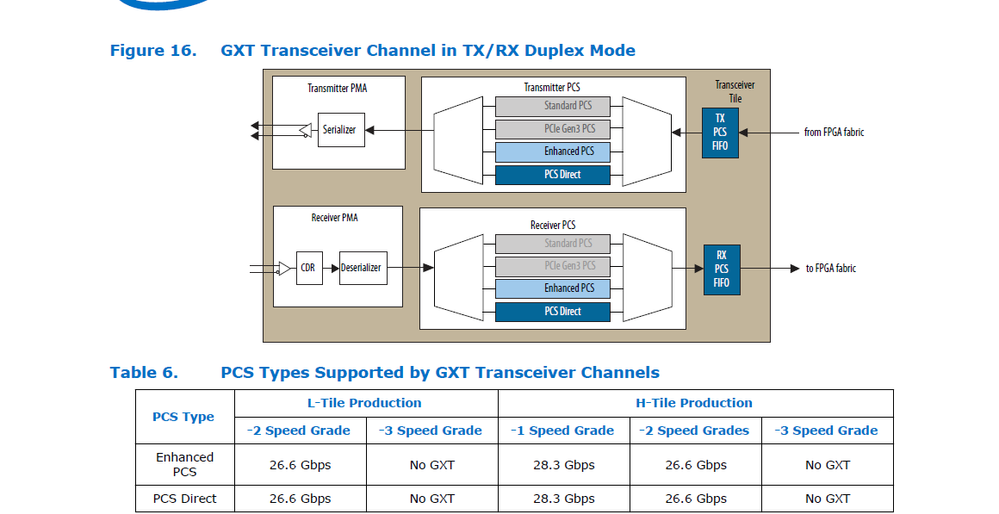

That's a good question. If you look at s10 SX/GX device overview datasheet and the part used in the s10 soc board(1SX280U) the X means that there are transceivers working at 28.3Gbps maximum.

GXT channels can achieve this, and GX ones can run up to 17Gbps.

In the manual of the demo board, there are 8 GXT Channels on FMCA port and 8 other GXT channels on FMCB.

I guess you will have to buy a FMC daughter card with SMA connectors for your test bench.

Also, have a look to stratix 10 datasheet, everything is explained about transceivers (E-Tile, H-Tile and L-tile)

Hope it helped,

regards,

John