- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

My design contains a DDR4(discrete component) EMIF, and I terminate the address/command/clk in the same way with Arria10 development kit DDR4 daughter card(DIMM). Here're my questions:

- The address/command/clk should be pull-up to VTT after the last DDR4 SDRAM, what's the value of VTT? 1.2V or 0.6V? VTT in daughter card is 1.2V(VDD), but in some other example designs VTT=0.6V(VDD/2).

- In daughter card, a resistor connects between CK0_T and CK0_C, but no resistor used to pull up CK0_T and CK0_C to VTT, should I add pull-up resistor for CK0_T and CK0_C?

Thanks, regards.

Link kopiert

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi SYiwe,

Thank you for joining this Intel Community.

Please refer to my answer below:

- The address/command/clk should be pull-up to VTT after the last DDR4 SDRAM, what's the value of VTT? 1.2V or 0.6V? VTT in daughter card is 1.2V(VDD), but in some other example designs VTT=0.6V(VDD/2).

[Ans]: Terminate the DDR4 address, command, and control signals to VTT= 0.6V (VDD/2).

2. In daughter card, a resistor connects between CK0_T and CK0_C, but no resistor used to pull up CK0_T and CK0_C to VTT, should I add pull-up resistor for CK0_T and CK0_C?

[Ans]: No, no need to add resistor pull-up to VTT.

Hope this helps.

Thanks

Regards,

Aida

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Thank you for your answer. But I still have some doubts.

CK0_T/CK0_C is differential clock output from FPGA to drive DDR4, not the reference clock input to FPGA.

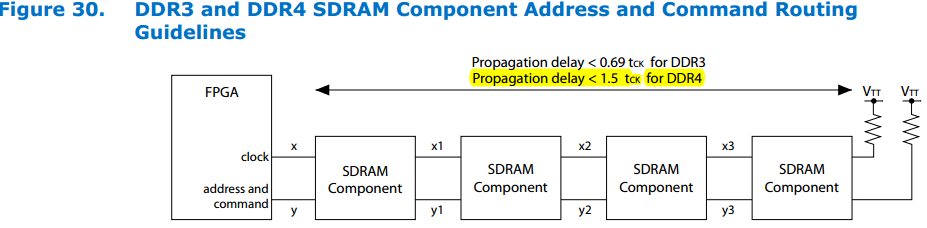

According to the following figure in user guide, CK0_T/CK0_C should be pull-up to VTT.

So I would like to confirm the following conclusion with you: there's no need to add pull-up resistor for CK0_T/CK0_C, is that correct?

Thanks, regards.

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi SYiwe,

Thank you for the diagram and sorry for the confusion. My bad, I was not referring to FPGA output clock at first.

Yes, the CK0_T/CK0_C should be terminate pull-up to VTT. You need to follow the terminationguidline based on the I/O standard you used.

Regards,

Aida

- RSS-Feed abonnieren

- Thema als neu kennzeichnen

- Thema als gelesen kennzeichnen

- Diesen Thema für aktuellen Benutzer floaten

- Lesezeichen

- Abonnieren

- Drucker-Anzeigeseite