- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

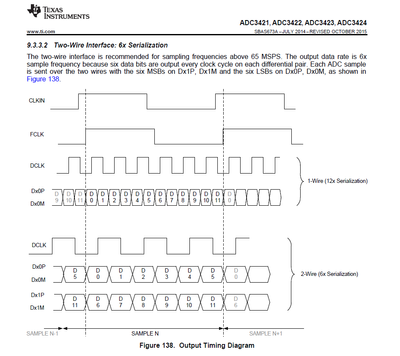

ADC: TI ADC3422 , 4 channel 12 bit ADC with 50M sample rate, LVDS

FPGA: Intel EP4CE15M9I7N

To read this ADC, so the clock should be as fast as 150MHz at rising and falling edge.

Is there any special IP as DDR RAM ALTPHY required?

Can EP4CE15M9I7N support four channels LVDS up to 150MHz read?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there

Since the LVDS support up to deserialization factor of 10, you can refer to link below to compute for other factors:

https://www.youtube.com/watch?v=02lgfcxSjQA

For the spec you mentioned, Cyclone IV shall be supported.

Thanks.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there

Since the LVDS support up to deserialization factor of 10, you can refer to link below to compute for other factors:

https://www.youtube.com/watch?v=02lgfcxSjQA

For the spec you mentioned, Cyclone IV shall be supported.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In adc spec, there is frame clock output, but I am not sure which signal in IP ALTLVDS_RX could match it?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page