- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I gather that two or more .sof files may be combined to a single .jic file and written to an active serial flash device using the Serial Flash Loader IP core. I am not clear on how the fpga can be triggered to re-configure itself from flash using one of the alternate images not located at address zero.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi tedh4ddv,

The Serial Flash Loader IP core is responsible for reading the selected bitstream from the flash memory at the specified address and configuring the FPGA accordingly.

Regards,

Fakhrul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

remote update IP has the function you are looking for. In the basic configuration, you are using different boot addresses for factory and application image, optionally you can change the boot address by a command.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi tedh4ddv,

The comment by FvM is accurate. If you wish to refresh the image from a particular address, please refer to the Intel® FPGA IP User Guide for Remote Update, accessible at this link: Remote Update Intel® FPGA IP User Guide.

Best regards,

Fakhrul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Currently the design provides the processor access to the serial configuration flash device via a SPI Flash Loader Platform (SPISlaveToAvalonMasterBridge and SPI_flash_platform_sfl_av_bridge). To utilize the Remote Update IP Core, I think the SPI_flash_platform_sfl_av_bridge should be removed, and the Remote Update IP Core would connect to the SPISlaveToAvalonMasterBridge via an Avalon MM interconnect. Does this sound reasonable?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi tedh4ddv,

My apologies as I overlooked your latest comment. You can refer Cyclone10 LP - Remote System Update Design Example as a reference for this application, there's also a diagram that you can refer to in the documentation as well: Cyclone 10 LP Remote System Upgrade Design Example User Guide.

Regards,

Fakhrul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@tedh4ddv wrote:Currently the design provides the processor access to the serial configuration flash device via a SPI Flash Loader Platform (SPISlaveToAvalonMasterBridge and SPI_flash_platform_sfl_av_bridge). To utilize the Remote Update IP Core, I think the SPI_flash_platform_sfl_av_bridge should be removed, and the Remote Update IP Core would connect to the SPISlaveToAvalonMasterBridge via an Avalon MM interconnect. Does this sound reasonable?

There are basically two tasks that have to be performed in an RSU aware design:- switching between different images during FPGA configuration load. That's the Remote Update IP task

- updating and verifying application image(s) in flash in FPGA user mode. This is achieved by a suitable flash loader IP, either using low level register or e.g. MM interface

Both components are usually separated in your design, in some cases remote update IP has an interface to flash to check image crc before loading it

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As I mentioned, we currently have a SPI_to_SerialFlashLoader platform in the design. We want to keep that function in place for loading new Flash images. When adding the SPI_to_RSU platform, which will be comprised of a SPI_To_AvalonMaster plus the RU Core, how is access to the Serial Flash interface handled? Do I require external multiplexing for the DCLK, DOUT, DIN and nCE pins? Or can the new SPI_to_RSU Platform handle both functions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Asking more simply, does the RSU Core handle the loading of a new .jic file into serial flash along with handling the switching between configurations?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

...or would I need to connect the Avalon output from the SPI_to_AvalonMaster core to both the Remote_Update core AND the AvalonSlave_to_SFL cores?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi tedh4ddv,

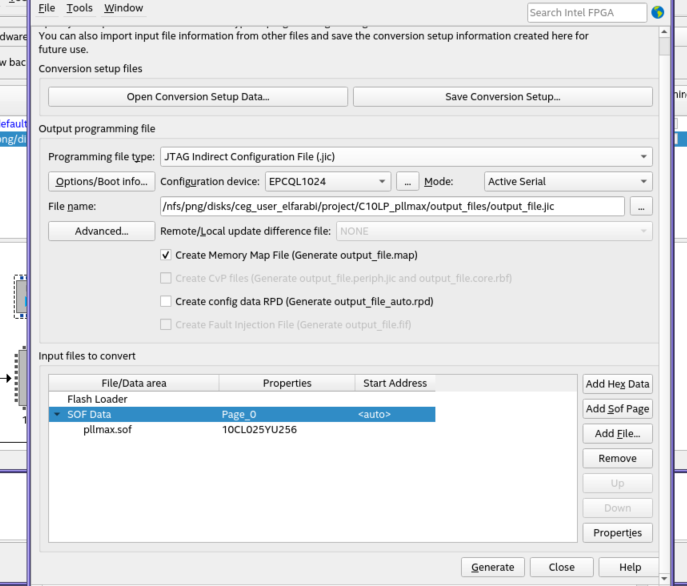

Following a discussion with my colleague, it appears that all you require is the SFL IP for your application. As illustrated below, when generating the .jic file using the "Convert Programming Files" tool, please make sure to leave the start address set to "auto," as shown below. This will enable the IP to autonomously configure the start address for your programming file, relieving you of any concerns in this regard.

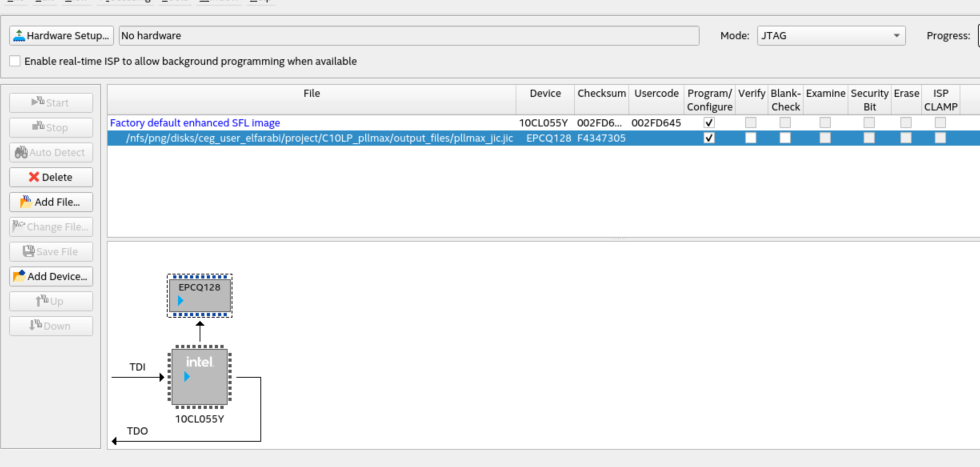

During the programming process, you'll notice that the SFL IP is automatically loaded, as demonstrated in the programmer interface below. For more detailed information, please consult the accompanying user guide: 1.3. Programming Single and Multiple Serial Configuration Devices with the Intel® FPGA Serial Flash Loader IP Core

Best regards,

Fakhrul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As we do not receive any response from you to the previous answer that we provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you. If you feel your support experience was less than a 9 or 10, please allow me to correct it before closing or please let me know the cause so that I may improve your future support experience

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page