- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When I follow the directions in (https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_a10_pcie_avmm_dma.pdf) section 2.2 I get the error:

# ** Error (suppressible): (vsim-3584) ./../../altera_pcie_a10_hip_181/sim/altpcie_a10_hip_pipen1b.v(2878): Module parameter 'eco_fb332688_dis' not found for override.

# Time: 0 ps Iteration: 0 Instance: /ep_g3x8_avmm256_integrated_tb/ep_g3x8_avmm256_integrated_inst/dut/altpcie_a10_hip_pipen1b File: ./../../altera_pcie_a10_hip_181/sim/altpcie_a10_hip_pipen1b.v

# Error loading designWhen I go into the offending file and comment out the line as such:

.avmm_power_iso_en_csr_ctrl (avmm_power_iso_en_csr_ctrl )

// .eco_fb332688_dis (eco_fb332688_dis )I can then simulate. I don't know if I am simulating correctly with that line commented out or not--or even what that line does. Anybody have any insight?

- Tags:

- PCIe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks BGrat,

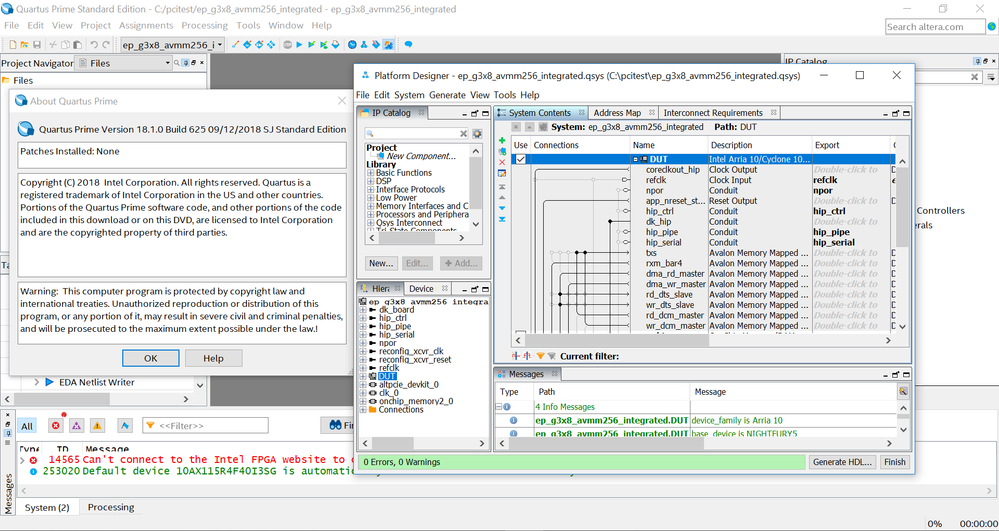

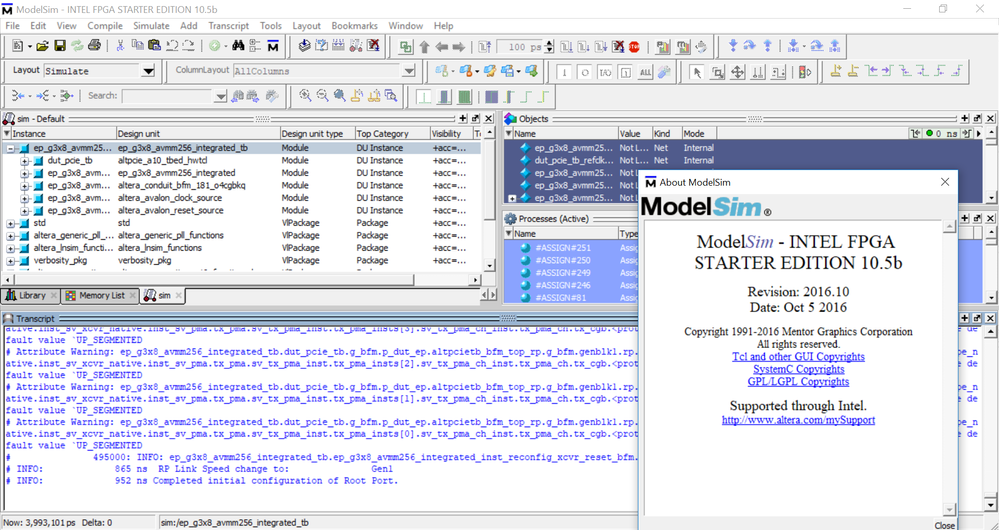

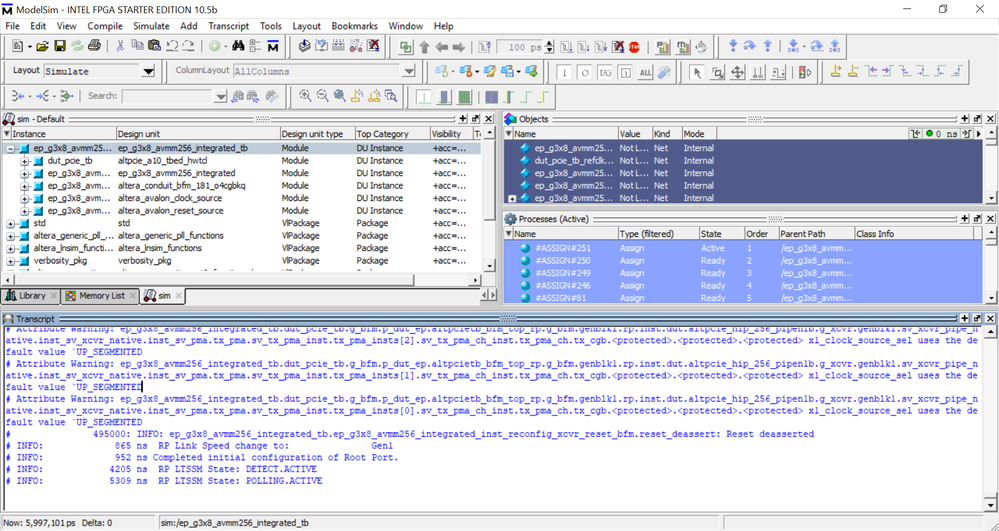

I was successfully able to simulate having same setup like Quartus 18.1 std with Modelsim 10.5b SE. Attached image

- Working directory need to be small as possible.

- Have same project name for project ep_g3x8_avmm256_integrated

- Open ep_g3x8_avmm256_integrated.qsys and Click Generate -> Generate Testbench System

or try by recreating the project.

Follow exact steps given in the document section 2.2 and 2.3.

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Regards

Anand

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I was trying to replicate the issues but not succeed can you please share the Quartus version & Edition used for the design?

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Anand,

In the Qsys file, it reports:

name="DUT_pcie_tb"

kind="altera_pcie_a10_tbed"

version="18.1"

It is the standard version (not Pro).

ModelSim-Intel FPGA Starter Edition 10.5b

Revision 2016.10

Date Oct. 5 2016

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks BGrat,

I was successfully able to simulate having same setup like Quartus 18.1 std with Modelsim 10.5b SE. Attached image

- Working directory need to be small as possible.

- Have same project name for project ep_g3x8_avmm256_integrated

- Open ep_g3x8_avmm256_integrated.qsys and Click Generate -> Generate Testbench System

or try by recreating the project.

Follow exact steps given in the document section 2.2 and 2.3.

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page