- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm trying to implement altera_lvds IP core in Arria10 device, and using modelsim to check behavior before implementing to hardware. The target is establishing a simple loopback function with following setup:

- Quartus version: Prime Pro 18.1

- ALTLVDS_Tx IP-Core

- Funtion Mode: Tx

- Number of channel: 2

- Data Rate: 600Mbps

- SerDes Factor: 6

- PLL Setting: Internal PLL, inclock=100MHz

- Tx core register is clocked by "tx_coreclock"

- Desired tx_outclock phase shift: 0 degree

- Tx_outclock division factor: 6

- ALTLVDS_Rx IP-core

- Functional Mode: Rx Non-DPA

- Number of channel: 2

- Data Rate: 600 Mbps

- SerDes Factor: 6

- PLL setting: Internal, inclock=100MHz

- Desired receiver inclock phase shift: 0 degree

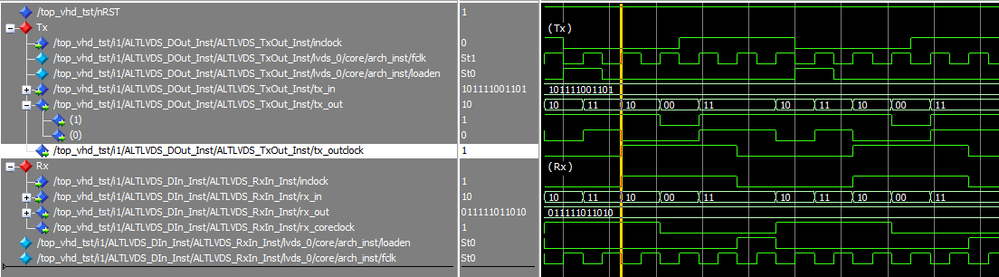

In quaruts project, I've initiated these two instance and connect tx_out[1:0]/tx_outclock of ALTLVDS_Tx to rx_in[1:0]/rx_inclock of ALTLVDS_Rx accordingly in modelsim testbench, so I should be able to see loopback parallel data from rx_out[11:0] port of ALTLVDS_Rx.

However, the waveform in modelsim wasn't exactly the same as what I expected. I have a "0° Edge Aligned tx_outclock x6 Serializer Waveform with Division Factor of 6 " in modelsim, which is incidental as user guide described. (page 20, figure 7, https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_altera_lvds.pdf)

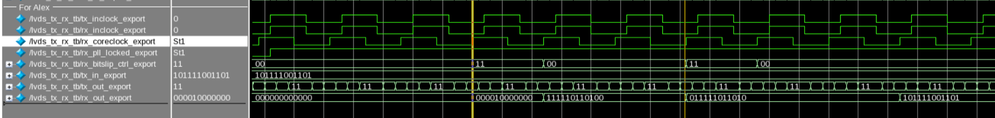

Here in ALTLVDS_Tx I have a fixed 12 bit value 0xBCD for test. In above waveform, we can see 0xBCD is decomposed into 2 serial data lane within a tx_outclock cycle.

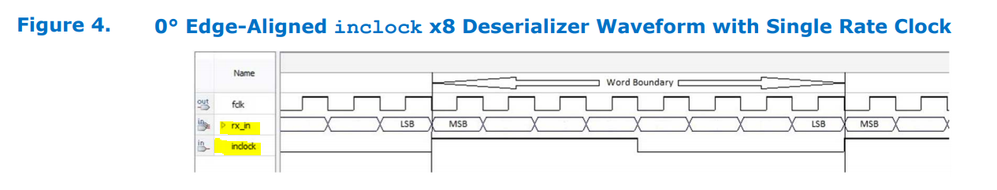

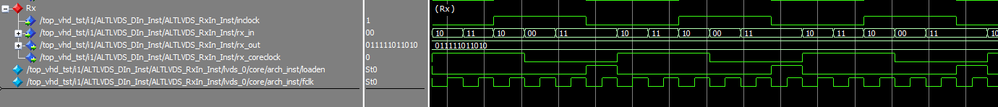

In the ALTLVDS_Rx side, the inclock and data phase relationship is intact and remains "0° Edge-Aligned inclock x6 Deserializer Waveform with Single Rate Clock", similar as waveform in user guide below:

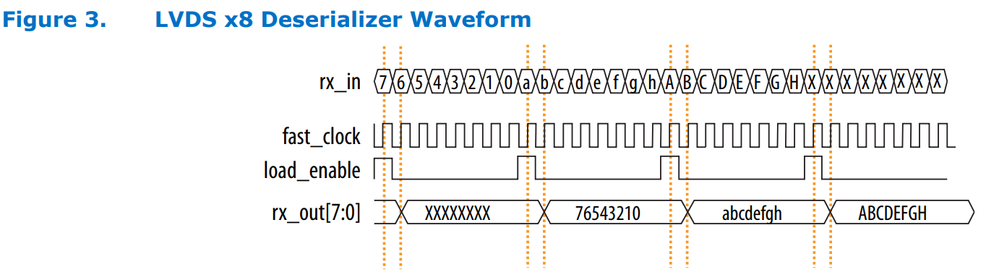

But somehow the rx_out[11:0] I got is not the fixed value I sent in ALTLVDS_Tx side. looks like there's bit shift occurs within ALTLVDS_Rx core. What makes me confused is, I though my case should be the simplest scenario of LVDS IP-core loopback, but not working. The inclock of Rx side is the "frame clock" of data, by using this as Rx internal PLL reference, it should work as word aligner and user doesn't need to do any bitslip or link training logic.

Plus, by checking modelsim waveform, the behavior doesn't matched with Figure 3 in user guide. If I follow Figure 3's logic, I got totally different output result of rx_out[11:0].

I've tried to tune "Desired receiver inclock phase shift" value of ALTLVDS_Rx IP core, and it did effect the rx_out[11:0] value, but still I can't have correct pattern I expected.

Could Intel support team have advice?

Thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alex

Let me review your inquiry and keep you posted once I have any update on this.

Thanks

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alex,

Can you share with us your sample design and testbench so that we can duplicate what you are seeing?

Thanks

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

June 12, 2020 at 12:18 PM

Actions for this Feed Item Comment

Thanks Alex. Do let us know if you need further help on this topic.

Eng Wei

Alex Huang (Customer)

June 12, 2020 at 12:07 PM

Actions for this Feed Item Comment

Hi Wei,

No worries, I can try to build a HDL for bitslip with reference doc.

Thanks again for your support, I believe you can close this case now

Alex

June 12, 2020 at 12:00 PM

Hi Alex

Unfortunately I can't find any design example from my side. But the explanation on the bitslip requirement seems accurate here where I used it in my testbench.

Section 5.6.5.1.3. Data Realignment Block (Bit Slip)

https://www.intel.com/content/www/us/en/programmable/documentation/sam1403483633377.html#sam1403482391636

For actual usage, we can create a comparison logic to enable bitslip until it locked to the correct pattern before we start accepting functional Rx input.

I can work with you on the design but I personally more comfortable with verilog coding instead of VHDL.

Thanks.

Eng Wei

Alex Huang (Customer)

June 11, 2020 at 7:16 AM

Actions for this Feed Item Comment

Hi Wei,

Got it. It's good to know that we'd better to have Rx block trained before use it. Does Intel has any reference/example design regarding link training by any chance?

Thanks,

Alex

Open Eng Wei Oh Preview

June 10, 2020 at 6:45 PM

Actions for this Feed Item Comment

Hi Alex

It is recommended to perform bit alignment with training pattern before putting the Rx block into functional. The good thing of the test pattern is that we can do delay on a per channel basis to confirm that all the channels are functional.

Thanks.

Eng Wei

Alex Huang (Customer)

Post

To: All

Actions for this Feed Item

Hi Wei,

No worries, thanks for your time.

And yes, looks like bitslip is way to go. But it confused me since currently I'm doing simulation in modelsim only, I thought the result I got should be an "ideal" one, no need to add extra bitslip effort on it. Like you said, mostly this feature is used for channel-to-channel skew.

Could you help me out to clarify my concept?

Thanks

Post

To: All

Actions for this Feed Item

Hi Alex

I am sorry for delaying the response as I am trying to understand your design, reproduce the issue and figuring the solution for it after long holidays.

I am implementing the similar design with similar tx's input. At the rx side, I am adding 2 bitslip pulses to realign the bits accordingly.

The 2 pulses is aligning the 6 MSB and 6 LSB accordingly, from 111110_110100 -> 011111_011010 -> 101111_001101.

Bitslip is used to compensate for this channel-to-channel skew and establish the correct received word boundary at each channel. For more information, we can refer to https://www.intel.com/content/www/us/en/programmable/documentation/sam1403483633377.html#sam1403482391636

Thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Copying the replies here before closing the ticket. Thanks all.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page