- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am working on Cyclone IV GX, for multi-instances on Triple Rate SDI.

Now I found reference design on loop out, that's fine.

But I need multi-instances on my project.

Do you have any data on how to ?

Thank you!

Regards,

Johnson

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chee Pin,

Thanks for getting back.

My question is about multi-instance TR SDI, especially reconfiguration.

The project needs 2 instances and each can work independently, 2 sets TR SDI Rx/ Tx, both channels can operate at different rate.

Target device is "EP4CGX30CF23C7",

And I instantiate 2 SDI Rx and 1 SDI Tx all at Triple Rate.

If all the SDIs feed the same clock source, then full compilation is passed.

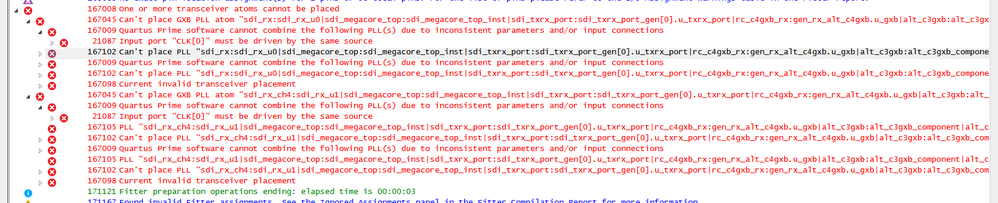

But once I add another clock as source for Rx, Quartus complaint about not able to fit into the device.

As I realized, this device has 2 MPLL on left block which could be used for transceiver.

Any idea about how I could overcome this problem?

Thank you!

Regards,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chee Pin,

1 MPLL has been used in 2Rx and 1Tx, PLL_5.

Also the SDI Tx uses a GPLL, PLL_1.

There's only 1 PLL left in the design.

The clock pin was M11/ N11 for this.

I have another clock locates at M7/ N7.

But can't be used in fitter.

FYI!

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi CP,

Thanks for the share.

I would like to know further about the real application.

2 instances of TR SDI, each will operate loop out the input data independently..

How many PLL is required, MPLL/ GPLL ?

Regards,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page