- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm using a Cyclone V-SE and trying to implement a HMC targetting a DDR3-800. After plugging in all the values from the vendor datasheet and running the whole compilation flow I can't get the design to meet timing (DDR Read Capture hold constraint fails miserably).

First of all I want to know if this is actually possible. If so, what are the main parameters used in the Read Capture setup/hold analysis?

Kind regards

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Just to make sure your device can support this, fill out the spec estimator and check the results:

Since you're using an SoC device, are you using the HPS hard controller, an FPGA hard controller, or a soft controller?

Are you running your user logic half-rate or quarter rate (if supported for your particular configuration)?

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @sstrell

I've checked the link and in principle I should be able to run DDR3-800 (400MHz)

I've got the HPS running at DDR3-800 without a problem. However I also want to use the FPGA HMC and drive another DDR3-800 memory chip. However, after pluggin in the values from the manufacturer, the Read Capture hold analysis has a 7 ps violation.

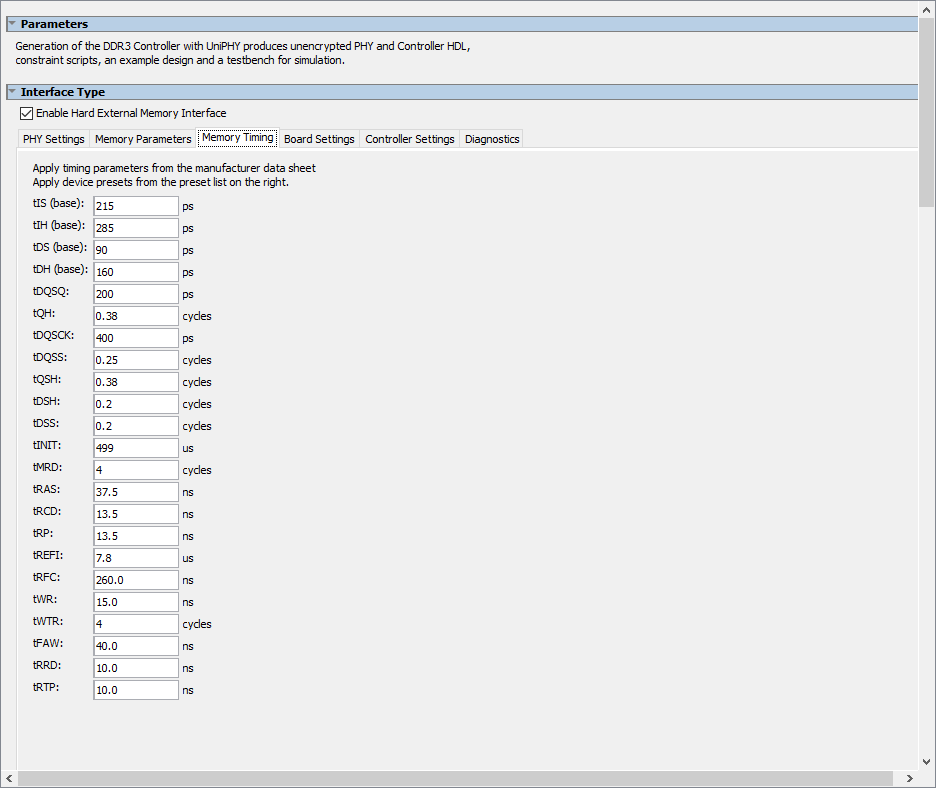

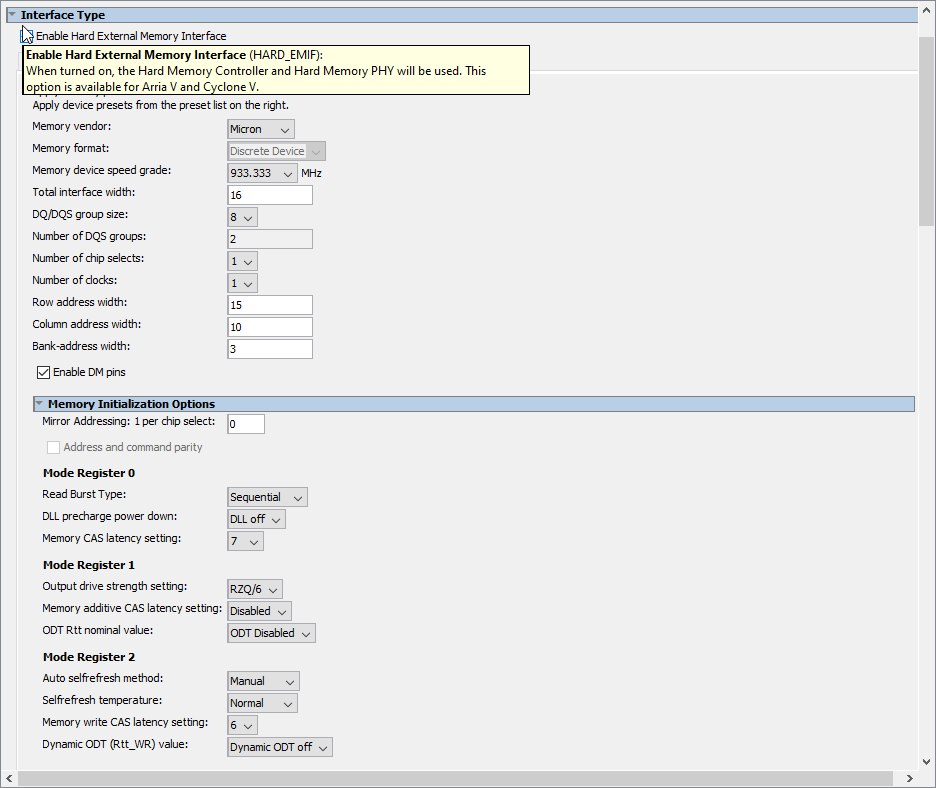

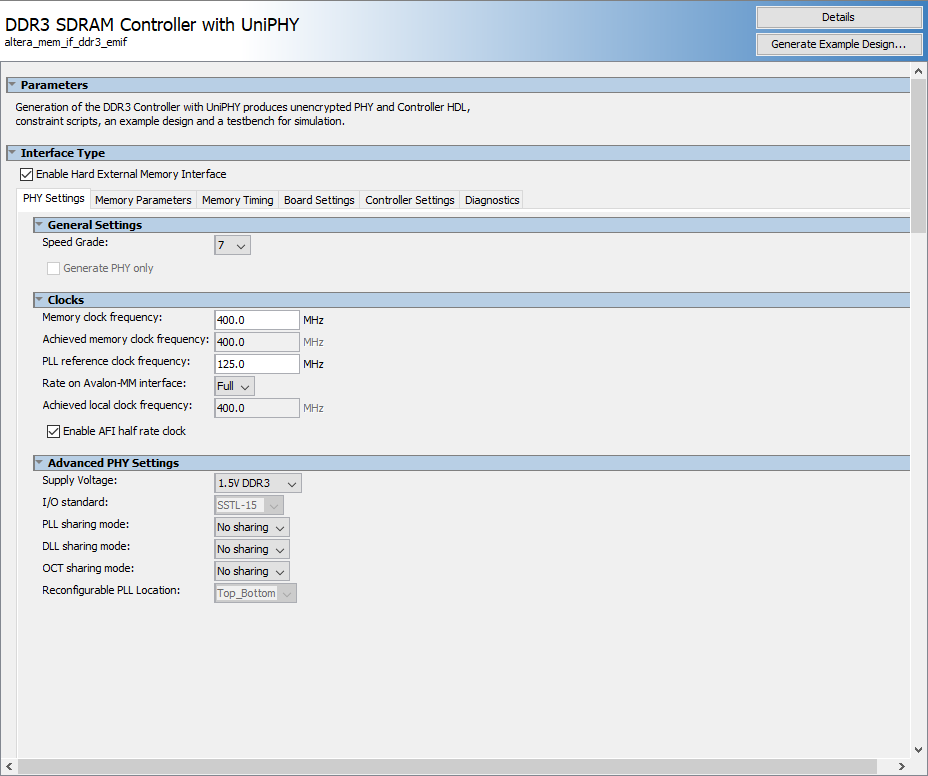

In principle, the HMC for Cyclone V only allows full data rate on the user logic. I've included the current configuration (maybe you can spot what's the issue)

Cheers.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you provide the design.qar for investigation?

Thanks.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page