- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

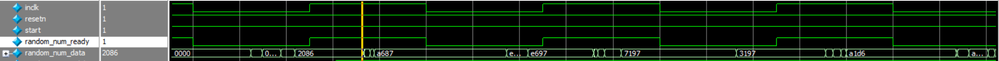

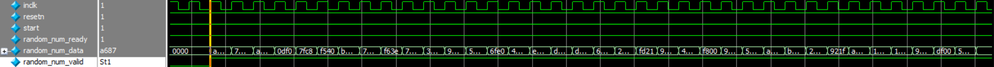

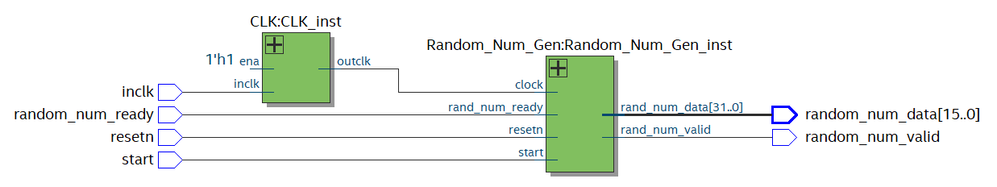

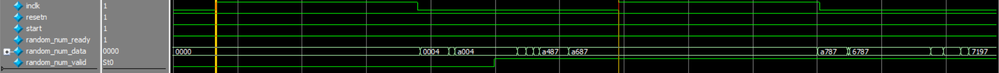

Simulate the Random Number Generator IP Core with ModelSim. The same testbench, when choosing different devices, the simulation results of rand_num_data are quite different.

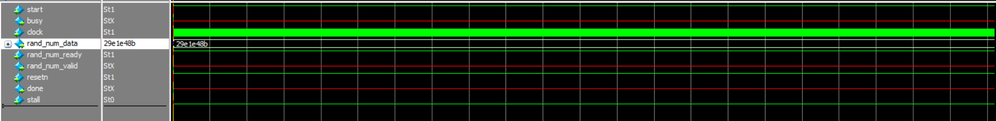

(1) When stratix iv (EP4SGX230KF40I3) is selected, rand_num_data is not synchronized with inclk. And when the clock frequency is increased to 320MHz, rand_num_data will have an indeterminate state Z.

(2) When Arria 10 (10AX027H4F34I3SG) is selected, rand_num_data is synchronized with inclk. And when the clock frequency is increased to 320MHz, rand_num_data is still output normally.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

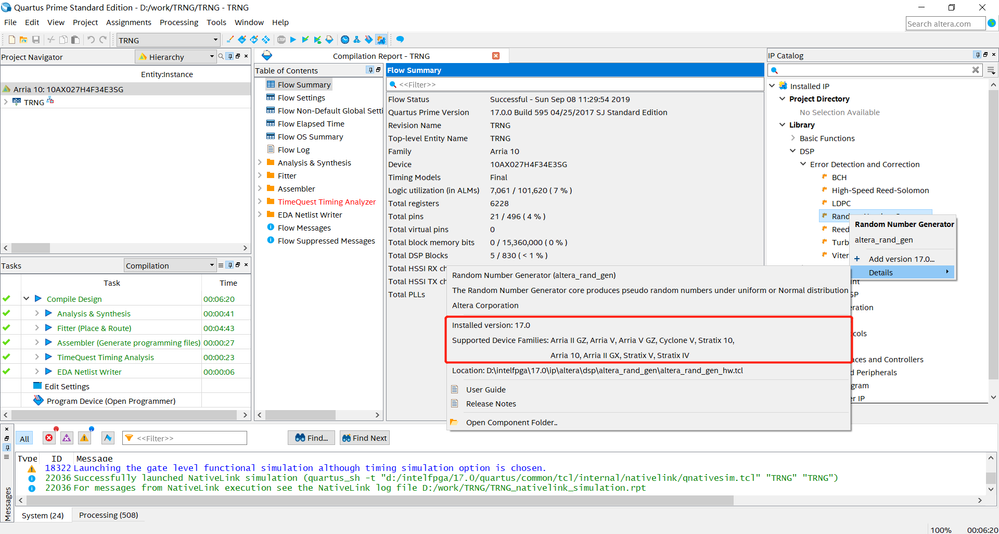

I will add some explanations. Quartus Prime Standard 17.0 is used. And the following picture shows the device families the IP core supported. Including Arria II GZ, Arria V, Arria V GZ, Cyclone V, Stratix 10, Arria 10, Arria II GX, Stratix V and Stratix IV.

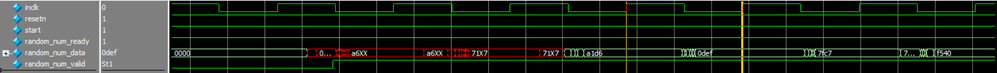

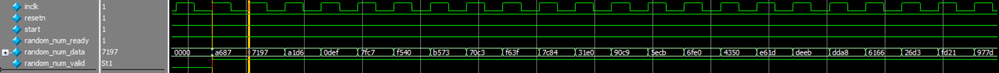

1、stratix iv simulation record:

① inclk is 3.124 ns:

③ inclk is 1000 ns:

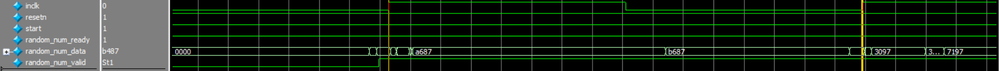

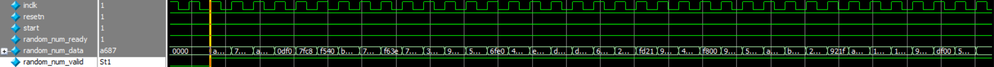

2、arria ii simulation record: inclk is 3.124 ns,

① arria_ii_GZ:

② arria_ii_GX:

There was no improvement in frequency reduction and replacement speed grade.

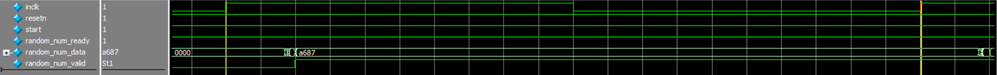

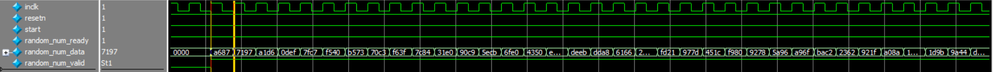

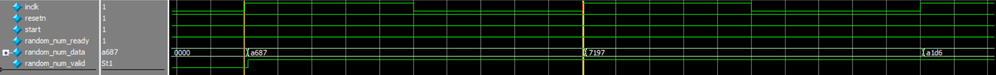

3、stratix v、arria 10、cyclone v simulation record: inclk is 3.124 ns,

① stratix v:

② arria 10:

③ cyclone v:

So, I want to determine if stratix iv can use the random number generator IP core. If I can use it, do I need some specific settings? Or is these different results caused by the quartus version?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As I understand it, you observe some issue with the SIV random number generator IP in Modelsim simulation where at 320MHz, there seems to be Z at the output. To facilitate further debugging, would you mind to share with me a simple test design and test bench which could replicate the observation? Please share with me the specific Quartus version that you are using as well.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Quartus Prime Standard 17.0 is used. There are two main problems in modelsim simulation of random number generator, when using EP4SGX230KF40I3.

(1) The output (rand_num_data) is not synchronized with inclk.

(2) When the clock frequency is increased to 320MHz, the output (rand_num_data) will have an indeterminate state Z.

But, when using qsim, there are no problems appear.

The attachment is the project files.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your update and sharing of the files. When you are referring to "qsim", just would like to check with you if you are referring to another simulator other than Modelsim? If yes, this may be help to further narrow down the issue.

Just would like to check with you if you have had a chance to try at SIV hardware to see if similar issue occur? This could help to isolate from simulation and also could act as a workaround for you to proceed with SIV design.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just would like to follow up with you on my previous inquiries. Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just to update you on the latest debugging finding from my side. For your information, I have created a simple simulation design in SIV and A10 in Q17.0Std for issue replication.

The following are my observations:

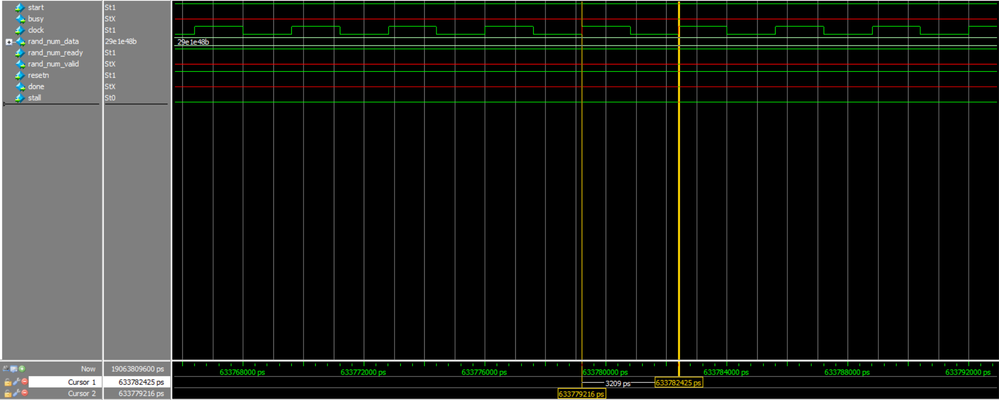

1. In SIV simulation, I observe that the rand_num_data is rising-edge aligned with clock. The similar observation applies to A10 simulation as well where the output dat ais rising-edge aligned with clock.

2. For your information, as I further look into your SIV simulation screenshot and compare with your A10 simulation and my SIV/A10 simulations, I observe that your rand_num_ready backpressure input signal in SIV simulation seems to be toggling together with the inclk. In your A10 simulation and my simulations, the rand_num_ready seems to be always high. I believe due to the backpressure signal, somehow it cause your simulation to be not rising edge aligned. Would you mind to edit your test bench to tied rand_num_ready to high to see if it helps?

3. I also observe in my simulations when the clock frequency is getting higher ie >300MHz, the output will become invalid. When I lower down the frequency, then the output is back to normal. I believe this is due to the limitation of the simulation model. As a workaround, you can perform functional simulation at lower frequency then increase the frequency to your target frequency in hardware.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have uploaded more detailed simulation record in the first answer for this question. In the record, I set the rand_num_ready to be always high. But it has no effect.

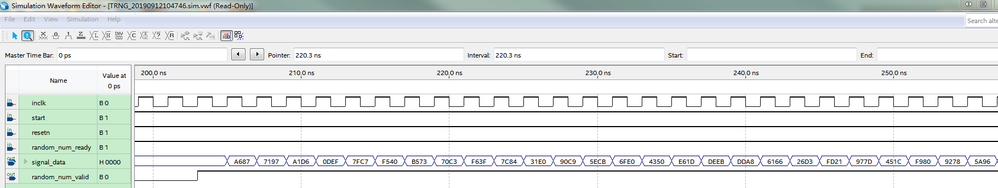

And about the "qsim", it refers to "University Program VWF" in Quartus Prime software.

This picture shows the simulation results of ".vwf" file (when using Stratix IV in 500MHz).

And I want to know the reason for the differences of ".vwf" file and Modelsim simulation.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your update. For your information, I have sent you a simple SIV simulation design through email which I am using to test the SIV random number generator simulation in Q17.0Std. You may do the following to run the with Modelsim Intel FPGA Edition 10.5b:

1. Unzip the file

2. Open Modelsim and change directory to siv_randnum\siv_rand\simulation\mentor

3. Type "source msim_setup.tcl"

4. Type "ld" to compile

5. Type "do wave.do" to populate the waveform

5. Type "run -all" to start simulation

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

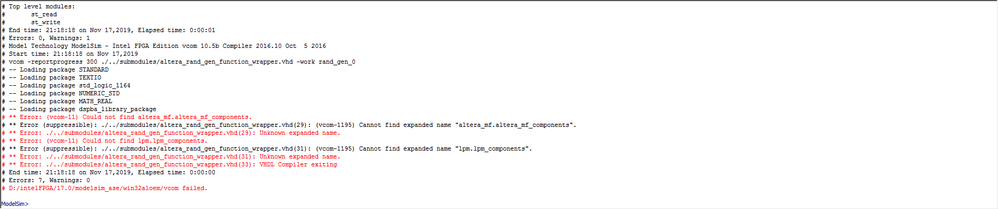

I follow the steps you gave. In the fourth step, the error is as follows: Error: (vcom-11) Could not find altera_mf.altera_mf_components.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry, I have not responded recently. About your "siv_randnum.zip" file, there are many errors when I type "ld" to compile. See the attached txt file for details.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Regarding your inquiry on "University Program VWF", sorry as I am not really familiar with this and could not comment further. Sorry for the inconvenience. Generally I will generate the IP and simulation model from Megawizard, create test bench and then run simulation in Modelsim.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your update. AS I understand it, you observe some issue when trying to run the simulation with the example that I shared to you. For your information, I have re-downloaded the zip sent to you and rerun the steps using Modelsim - Intel FPGA Edition 10.5b and the simulation seems to be working fine.

As I look into the error message that you have encountered, it seems to prompt about unable to compile "altera_mf_components.vhd". Based on my understanding from the msim_setup.tcl, if you are using Modelsim Intel FPGA Edition, it has built in library for this and the "ld" commands would not attempt to compile this library.

Just would like to check with you which specific Modelsim version that you are using to compile? If it is not Modelsim Intel FPGA Edition, you might need to edit the msim_setup.tcl to set the "QUARTUS_INSTALL_DIR" parameter correctly before you open and compile the files in Modelsim.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just would like to follow up with you on this. Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just would like to follow up with you on this. Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the delay. I have been out of office for the past week. Regarding your latest compilation error, it seems like the default built in library which suppose to be to available in the Modelsim Intel FPGA Edition could not be found during the compilation ie altera_mf.

I am not sure why your compilation is unable to locate these libraries but as a workaround, you can force compile all these libraries to your local folder. You can do the following in msim_setup.tcl:

1. Change "QUARTUS_INSTALL_DIR" to your local Quartus installation folder at line 114

2. Comment out "if ![ string match "*ModelSim ALTERA*" [ vsim -version ] ] {" at line 145 and its corresponding "}" at line 178

3. Commenout "if ![ string match "*ModelSim ALTERA*" [ vsim -version ] ] {" at line 186 and its corresponding "}" at line 215

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just would like to follow if the previous note on editing the msim_setup.tcl to compile libraries helps?

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have been changed the msim_setup.tcl. But, when I type "ld", there will appear many errors which are the same as before.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for sharing the msim_setup.tcl. I notice that you have commented all the libraries compilation related lines in the msim_setup.tcl. Sorry for any confiusion, please try to comment out only the following lines as in one of my previous notes:

1. Change "QUARTUS_INSTALL_DIR" to your local Quartus installation folder at line 114

2. Comment out "if ![ string match "*ModelSim ALTERA*" [ vsim -version ] ] {" at line 145 and its corresponding "}" at line 178

3. Commen out "if ![ string match "*ModelSim ALTERA*" [ vsim -version ] ] {" at line 186 and its corresponding "}" at line 215

Only 5 lines 114, 145, 178, 186 and 215 are to be commented out.

Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply. The simulation has been successfully implemented. But I noticed that the clock is 100MHz. I tried to increase the clock to 3200ps, there will be some other wrong with the results of simulation.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

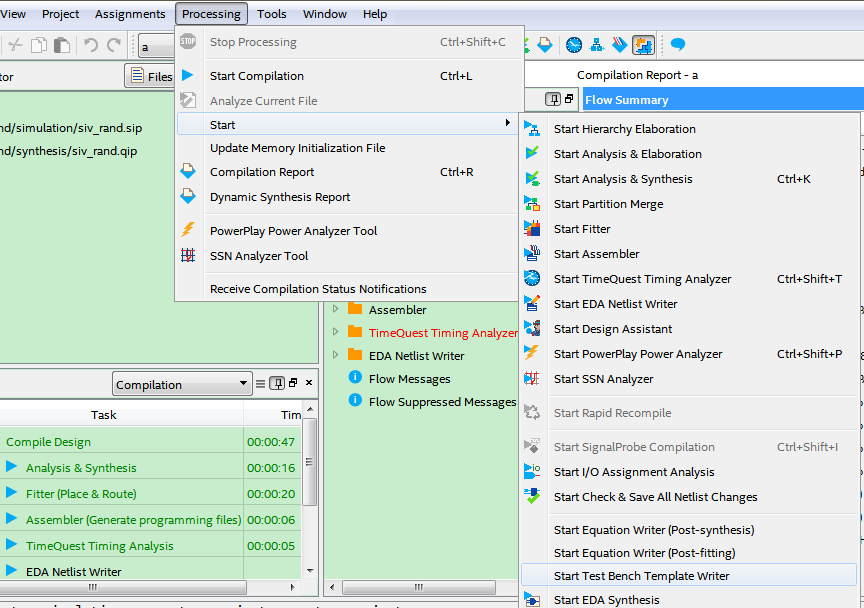

I want to simulate the quartus project containing random IP core. I followed the steps of "processing-start-start testbench template writer" but couldn't generate the testbench.

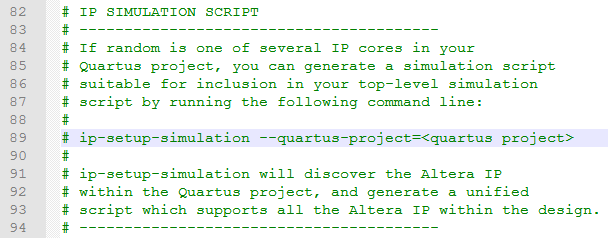

Then I saw a paragraph in msim_setup.tcl, as shown in the figure. But I'm not sure how to use "ip-setup-simulation --quartus-project = <quartus project>". When I type it in the tcl console in quartus, there will appear errors. When I input it in modelsim-altera, there also many errors.

Looking forward to your reply, thank you!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page