- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

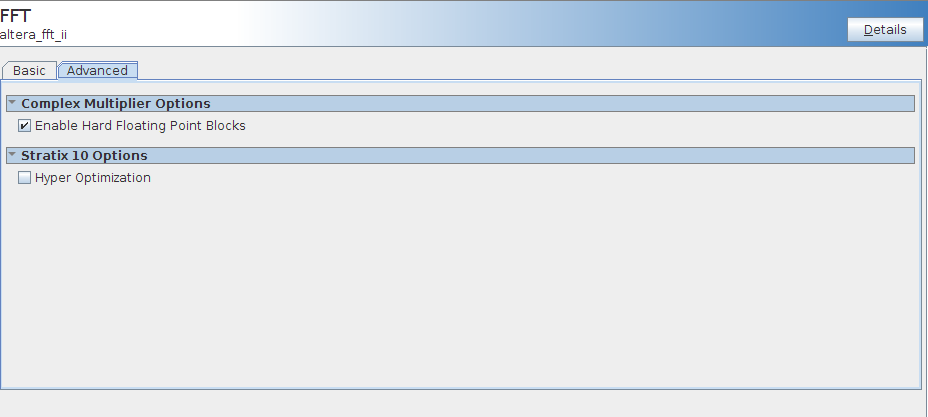

The FFT IP is not correctly behaving when the hard floating point blocks are enabled for arria 10 device.

When the option is disabled in the parameter editor the FFT block is working fine.

The FFT is configured for variable streaming , single precision floating point, 2048 point forward FFT,input and output order are natural.

I am giving a single 2048 time domain sample packet as input. The expected output should be 2048 samples in a single packet, which is not observed when hard floating point blocks are enabled.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chee Pin,

There are the answers to your queries

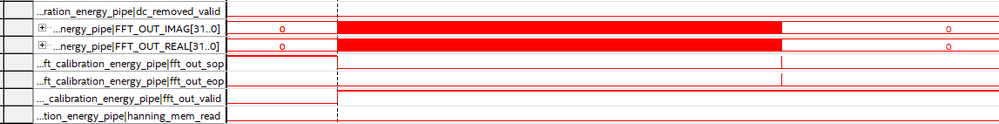

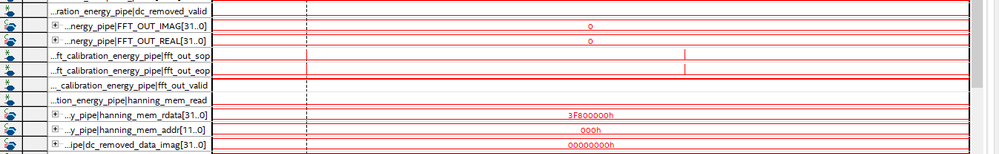

1) I am giving a single 2048 packet as input, a single 2048 packet output is expected. But the output has multiple sop and eop , the valid signal never goes down. The output data is also incorrect. Find the below screeshots

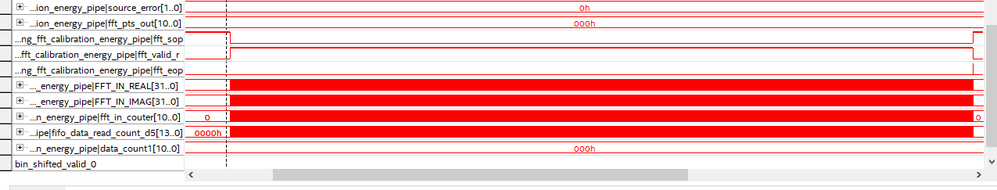

The input data i am givoing

The output i am getting

2) Quartus Prime pro 17.1.0

3) It is in the ip parameter editor gui

4) qsys is attached as a zip file

5) I am seeing this issue in hardware using signal tap.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page