- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

In the HDMI Sink, the DRMI packets are mapped to the Address 0x88 of the Auxiliary Packet Memory Map:

But, how can I send the DRMI packets through the HDMI source? What's port should be used?

Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You are referring to the Design Example for Arria 10, but I'm working with the Cyclone-10.

Instructions for Cyclone 10 DRMI Filtering are different:

but they are not compatible with the generated code...

The User Guide for Arria 10, which you are referring to, is compatible to the generated code, which I have in my project...

Anyway, I'll set the multiplexer_in0_valid signal to '0' according to your recommendation and let you know whether it works.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Any response?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi amildm,

Thank you for reaching out.

Just to let you know that Intel has received your support request and currently we are confirming the details with our internal team.

Allow me some time to look into your issue. I shall come back to you with findings.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks ZulsyafiqH_Intel! Looking forward to your findings...

You can think about the HDMI v1.4 to v2.1 Video Converter. There are two HDMI IPs inside of Cyclone 10 - the first one operates as a sink and receives HDMI v1.4 video stream, the second one should operate as an HDMI source and send the incoming video stream out in the HDMI v2.1 format. So, insertion of the DRMI packets to the incoming video stream is required. How should be this done?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

There is one more issue - then I connect two HDMI IPs back to back (according to Intel's Design Example) and stream video with DRMI to one of the HDMI interfaces (used as a sink/receiver), the second HDMI interface (used as a source/transmitter) sends the video stream with DRMI, which value is 12345678... What's wrong?

Here is the configuration:

Video with DRMI ---> HDMI IF -----> RXTXLink (same as in design example) -----> HDMI IF -----> Video with DRMI=12345678

Could the HDMI IF be configured for forwarding a constant value of DRMI=12345678 ???

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi amildm,

Good day.

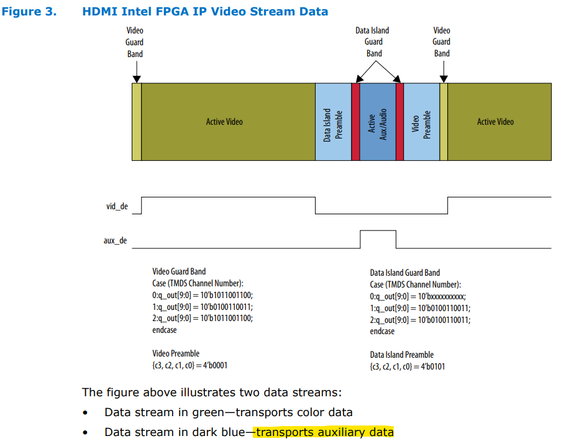

DRMI packets are part of the Auxiliary data. These data is place in packets and transferred using 3 main data channel.

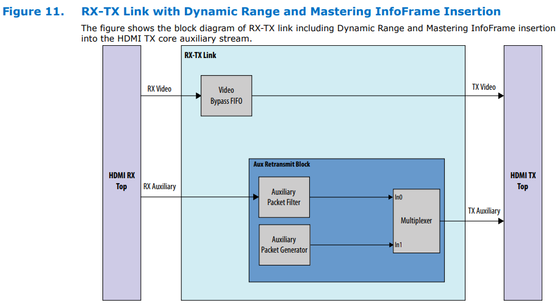

The reason that you are getting a constant value could be due to filtering mode.

In this case, when your source is transmitting the payload, the Aux packet filter the payload, and use the payload generated by the Aux packet generator.

There is a way to disable this filter as shown in picture below:

You may refer to below link for more information on said above:

HDMI Intel® FPGA IP User Guide - HDMI Overview

May I know what FPGA device are you using for your project?

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ZulsyafiqH_Intel, thanks a lot for your your response!

I'll try to deal with the Design Example for HDR, will let you know how it's going.

My project is based on the Cyclon-10 GX device, Quartus Pro v19.3.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

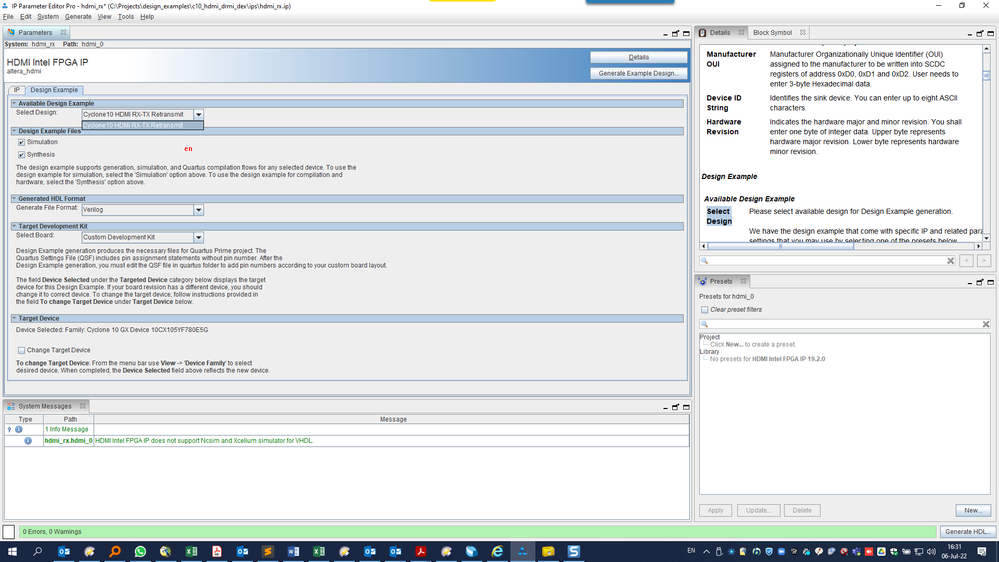

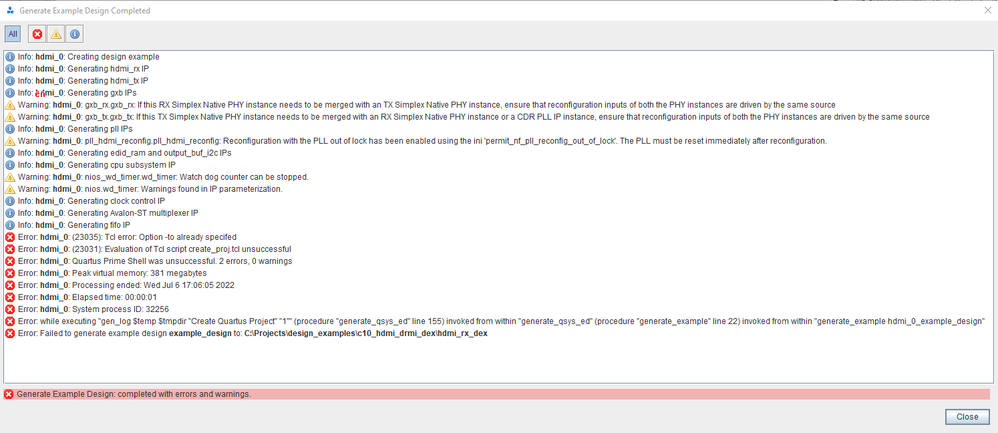

I've tried to generate the HDMI IP Design Example, but the generation has been failed with the following error:

------------------------------------------------------------------------------------------------------------------------------

------------------------------------------------------------------------------------------------------------------------------

------------------------------------------------------------------------------------------------------------------------------

Could you please help me with generation the HDMI Example Design for Quartus v19.3 ?

Attached please find the archived directory, where I tried to generate the Example Design.

Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

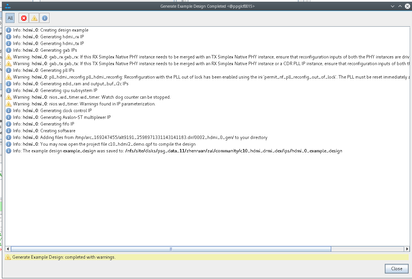

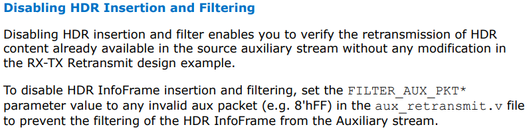

I've generated the HDMI Design Example for Cyclone-10, but the aux_retransmit.v file was not generated (not a part of the HDMI Example Design), so I cannot change there the FILTER_AUX_PKT* parameters there...

So, how to disable the HDR filtering if the mentioned file doesn't exist?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi amildm,

Good day.

We have downloaded your design.

Allow us some time to replicate the error from our side.

Once I manage to replicate, I shall come back to you with findings.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there,

Is there any progress with the Design Example?

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Is there any progress with my question? I need a response ASAP.

How can I disable the DRMI packets filtering in the Intel's Example Design? The file aux_retransmit.v was in not present among the generated files for the HDMI Example Design (generated for Cyclone-10).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi amildm,

Good day.

We manage to replicate the error from our side using your design but I believe this error is due to the top module C10_HDMI_DRMI_DEX is not included in the rar file. The rar file just includes the hdmi_rx ip and project setting file.

However, we also manage to generate Intel example design from our side with no error.

Regarding to the aux_retransmit.v file, we have confirm with our internal team that this file only exist for HDMI2.1(FRL) design.

At this point of time, Cyclone 10 does not support FRL mode.

With that, I can conclude that Cyclone 10 does not support HDR filtering.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As I mentioned in the beginning of the thread, I generated an Example Design of HDMI IF for Cyclone-10 and received the constant HDR values (1,2,3,4,5,...) as the metadata.

The answer, which I received in the thread, is so that these values (1,2,3,4,5,...) are due to the Filtering Mode of IP and I need to change parameters in the aux_retransmit.v file.

In the last post to the thread the answer was "Cyclone 10 does not support HDR filtering".

So, my question is very simple now: "what should I change in the HDMI IP Example Design for Cyclone-10 so it will pass through the incoming DRMI packets"?

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi amildm,

Good day.

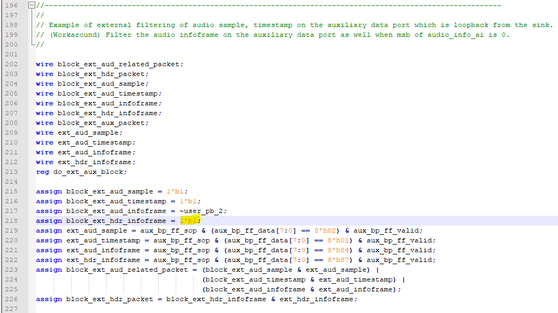

After further discussion with internal team, to passthrough HDR infoframe, you need to change below bit to 0 in the rxtx_link.v file located in the rtl folder.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ZulsyafiqH_Intel,

Thanks a lot to your response.

I'll do the mentioned by you change and test the design on the board.

I'll return to the office next week, so please be patient until my response.

Thank you again,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

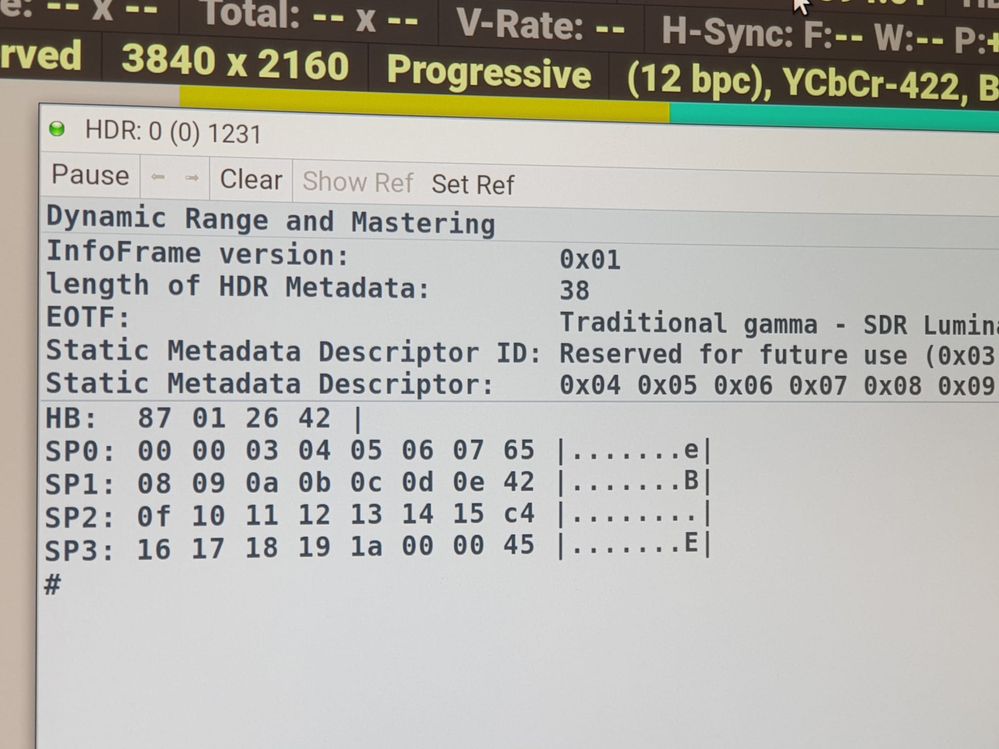

I've changed the mentioned block_ext_hdr_infoframe signal to drive '0', but still what's going out is the internally generated HDR metadata, not one which the video source sends.

Here is the HDR, which was received (captured by Quantum Data):

Should anything else be changed in the RTL in order to pass through the original DRMI frames with the original HDR metadata?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi amildm,

Good day.

I wish to follow up with you about this case.

Did you manage to passthrough HDR infoframe?

Hoping to hear back from you so that we can proceed for next step.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi amildm,

I wish to follow up with you on this case. Do you still have further inquiries on this issue? I will remain this loop open for 2 days.

If we do not receive any response from you to the previous answer that I have provided.

This thread will be transitioned to community support.

If you have a new question, feel free to open a new thread to get support from Intel experts.

Otherwise, the community users will continue to help you on this thread.

Thank you

Best Regards,

ZulsyafiqH_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm going to test the proposed configuration on the board till end of the week, so meanwhile please don't close the case, thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi amildm,

Thank you for the update.

>Should anything else be changed in the RTL in order to pass through the original DRMI frames with

>the original HDR metadata?

I have check with our internal team on this.

You may need to set multiplexer_in0_valid of the avalon_st_multiplexer instance in the altera_hdmi_aux_hdr.v file to 1'b0 to prevent the Auxiliary Packet Generator from forming and inserting additional HDR InfoFrame into the TX Auxiliary stream.

You may refer to below link for more information:

HDMI Intel® FPGA IP Design Example User Guide - Disabling HDR Insertion and Filtering

Best Regards,

ZulsyafiqH_Intel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page