- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

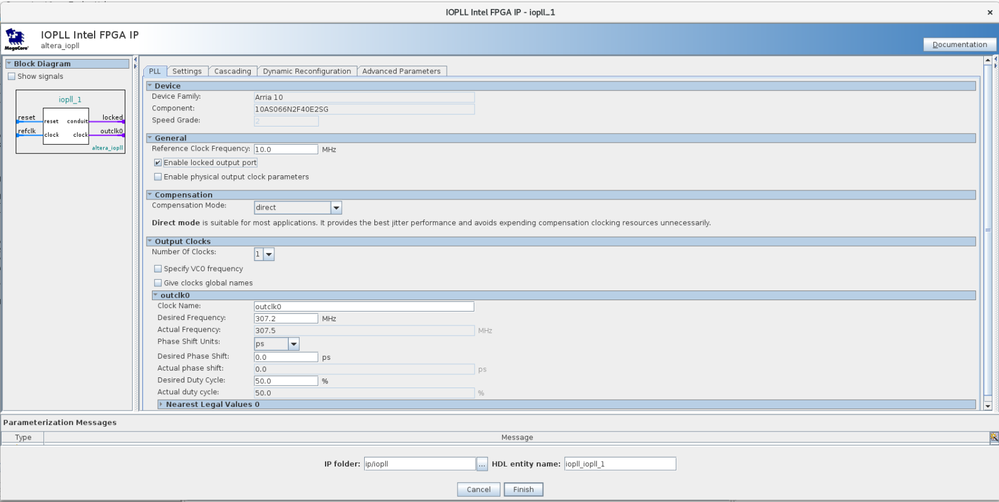

With many possible combinations as well, I could get Actual output clock as 307.5M/307.142M/307.189M but not exact value. M,N,C Counter values can be edited only as integer values but not fractional values. Please suggest what can be done.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Anamika

Sorry for late response. Can you try to set the PLL mode to Fractional-N PLL?

Thanks

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the response.

Actually, in IOPLL there is no option to set PLL mode as Fractional mode.

But there is one fPLL under Transceiver section in which we can use Fractional mode.

Is it ok to use fPLL for driving user logic?

When I tried using fPLL it is giving Fitter placement issues as shown below?

"Error(11215): Input port "REFCLK" of "CMU_FPLL_REFCLK_SELECT" cannot connect to PLD port "O" of "IO_INPUT_BUFFER" for atom "fpga_clk~input". "

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Anamika

May I know which version of Quartus tools that you are currently using?

For PLL selection, for example in Quartus 18.1 version, we can use:

Basic Functions -> PLL -> PLL Intel FPGA IP

After selecting the IP above, you can refer to doc below for more calculation setting:

https://www.intel.com/content/dam/altera-www/global/en_US/kdb/rd08062012_921/how_fractional_divisor_is_calculated_in_quartus_rev4.pdf

Thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eng Wei

I am using Quartus Prime 19.1.0 and Arria 10 SoC Device.

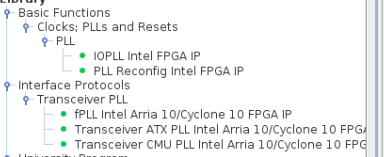

For PLL IP Selection, Basic Functions -> PLL -> IOPLL Intel FPGA IP as shown in the image attached.

For Parameter settings for IOPLL, please refer attached image.

Could you please check these snapshots and revert.

Thanks and Regards

Anamika Bhushan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Anamika Bhushan

For Arria 10 device, yup, you can use the fpll under Transceiver PLL. Regarding the fitter issue when you were using the fpll, can you share with us the parameter setting that you are using for the fpll? Or possibly a sample design that you are connecting the fpll?

Thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Eng Wei

I have created one simple counter logic, to make sure fPLL works for user logic. I have attached parameter selction pic for fPLL.

Clock path is FPGA pin -> fPLL input

Output clock from fPLL is used for running a 4 bit counter. Counter bits are given to on board LEDs.

Error: Error(11215): Input port "REFCLK" of "CMU_FPLL_REFCLK_SELECT" cannot connect to PLD port "O" of "IO_INPUT_BUFFER" for atom "fpga_clk~input".

Extra Info(13133): Output port's "O[0]" atom name is "fpga_clk~input".

Extra Info(13134): Input port's "REFCLK[0]" atom name is "u0|xcvr_fpll_a10_0|xcvr_fpll_a10_0|fpll_refclk_select_inst".

Extra Info(12877): Output port "O[0]" of "IO_INPUT_BUFFER" can connect to:

Extra Info(12878): Port "INCLK[0]" of "CLKBUFBLOCK"

Extra Info(12878): Port "INCLK[0]" of "CLKSELBLOCK"

Extra Info(12878): Port "INCLK[1]" of "CLKSELBLOCK"

Extra Info(12878): Port "INCLK[2]" of "CLKSELBLOCK"

Extra Info(12878): Port "INCLK[3]" of "CLKSELBLOCK"

Extra Info(12878): Port "DATAIN[0]" of "DELAY_CHAIN"

Extra Info(12878): Port "I_INCLK[0]" of "CLKBURSTBLOCK"

Extra Info(12878): Port "I_RXN[0]" of "HSSI_PMA_RX_BUF"

Extra Info(12878): Port "I_RXP[0]" of "HSSI_PMA_RX_BUF"

Extra Info(12878): Port "I_RX_N_BIDIR_IN[0]" of "HSSI_PMA_TX_BUF"

Extra Info(12878): Port "I_RX_P_BIDIR_IN[0]" of "HSSI_PMA_TX_BUF"

Extra Info(12878): Port "I_REFCLK_INN[0]" of "HSSI_REFCLK_DIVIDER"

Extra Info(12878): Port "I_REFCLK_INP[0]" of "HSSI_REFCLK_DIVIDER"

Extra Info(12878): Port "I_RXP[0]" of "HSSI_PMA_CDR_PLL"

Extra Info(12878): Port "I_PIN_PERST_N[0]" of "HSSI_GEN3_X8_PCIE_HIP"

Extra Info(12879): Input port "REFCLK[0]" of "CMU_FPLL_REFCLK_SELECT" can connect to:

Extra Info(12880): Port "O_REFCLK_A[0]" of "HSSI_REFCLK_DIVIDER"

Anamika Bhushan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Anamika Bhushan

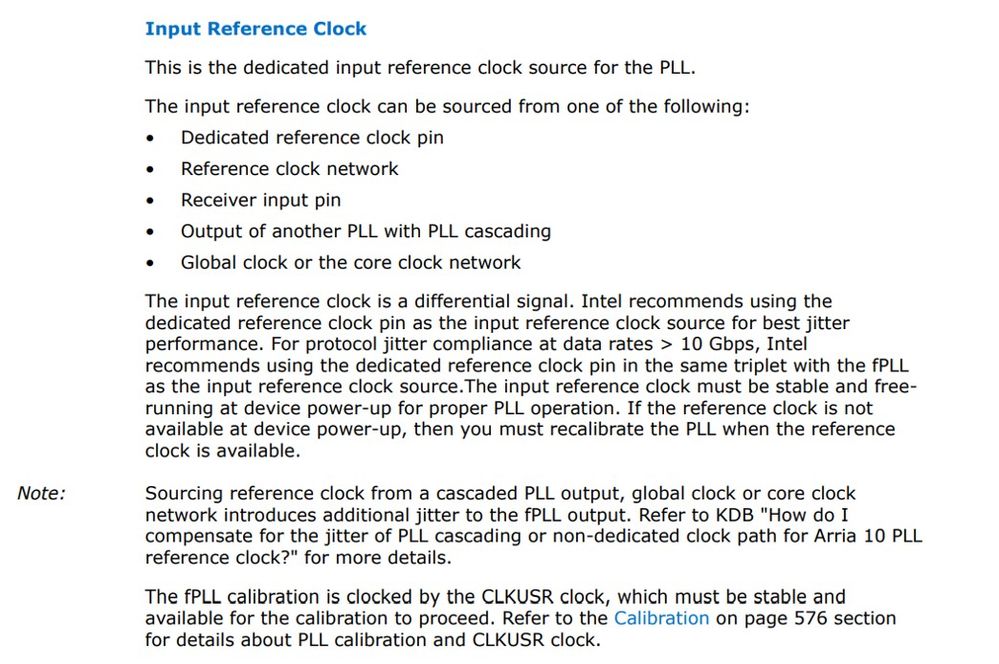

We can refer to the doc below (Section 3.1.3. fPLL) to check if we met the input reference clock spec for the fpll:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/arria-10/ug_arria10_xcvr_phy.pdf

Fitter will prompt error when certain conditions are not met.

Thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Anamika Bhushan

We do not receive any response from you to the previous reply that we have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Eng Wei

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page