- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Dear Support and Expert,

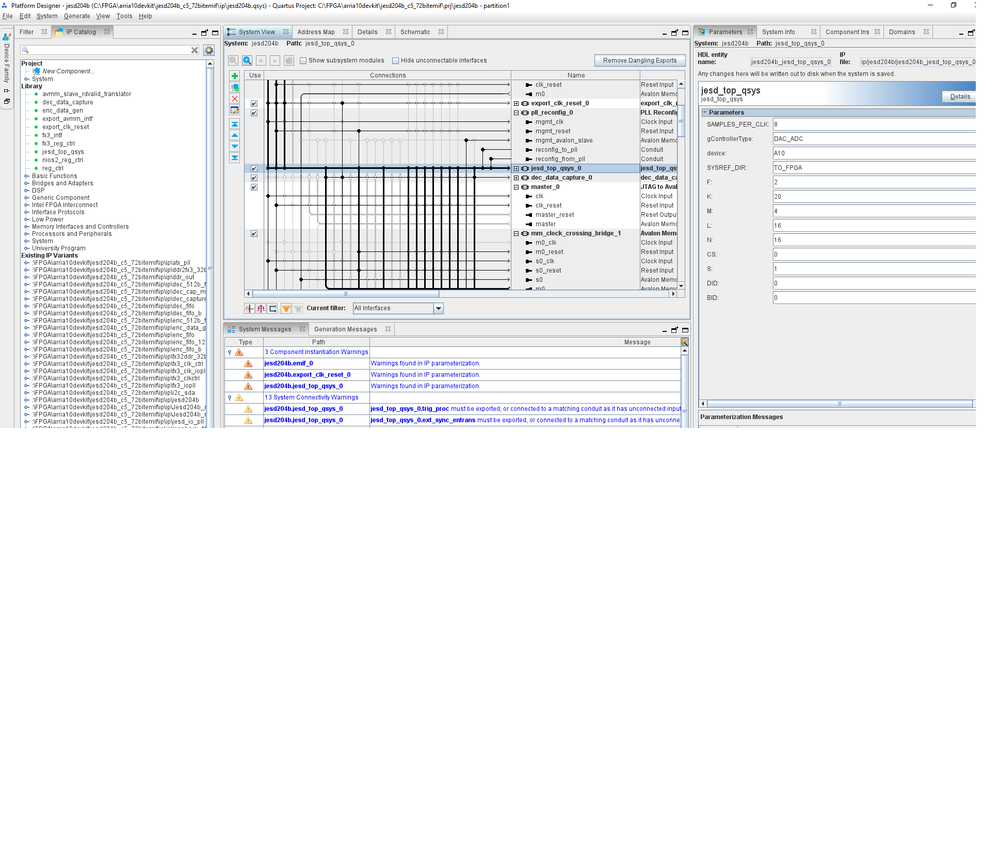

While I am reading the "JESD204B Intel® FPGA IP User Guide" 21.3.

it claims in the core features "• Single or multiple lanes (up to 8 lanes per link)"

I don't quite understand this 8 lanes per link limit.

I have a design from Texas Instrument, the parameters of the IP core use 16 lanes in 1 link(I guess).

can anyone familiar with JESD204B core, give me some suggestion. how to understand the 8 lane per link limit.

thank you,

David

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi David,

Good Day.

Thank you for your patience.

You may refer to chapter 2.3, and 2.5 of the JESD204B Intel FPGA IP User Guide for more details.

I believe you are talking is the Lanes per converter device.

In your case, your project require 16 lanes, hence, you will need 2 converters.

Thank you.

Best Regards,

ZulsyafiqH_Intel

Ссылка скопирована

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

the IP I mentioned above is a customer IP, sorry for asking a silly question.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi David,

Good Day.

Thank you for your patience.

You may refer to chapter 2.3, and 2.5 of the JESD204B Intel FPGA IP User Guide for more details.

I believe you are talking is the Lanes per converter device.

In your case, your project require 16 lanes, hence, you will need 2 converters.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi David,

Below is the link to JESD204B Intel FPGA IP User Guide:

JESD204B Intel® FPGA IP User Guide

Below here is the link to AN803 documentation. Under documentation, you may refer to figure 3 & 4 for examples of converters:

AN803: Implementing Unsynchronized ADC Multi-Link Design with JESD204B RX IP Core

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi David,

We do not receive any response from you to the previous reply that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread.

Thank you.

Best Regards,

ZulsyafiqH_Intel

- Подписка на RSS-канал

- Отметить тему как новую

- Отметить тему как прочитанную

- Выполнить отслеживание данной Тема для текущего пользователя

- Закладка

- Подписаться

- Страница в формате печати