- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi

I have task to transmit data from 1 board to another

Each board has FPGA stratix 10M

To do it - I use LVDS SERDES IP in FPGA (TX) and other LVDS SERDES IP in FPGA (RX)

All the pins define as LVDS (including clocks & data)

My problem is : Sometimes pll lock flag doesn't lock

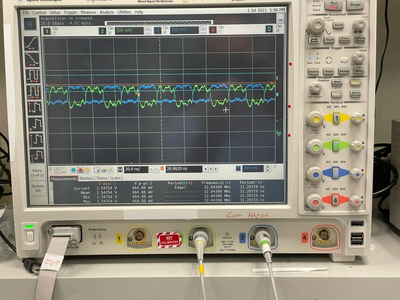

I don't know what is root casue for that - but I sample the clocks by scope

You can find it in the attached pic :

Do I need change the IO standard ?

Do I need change the internal termination ?

BR,

Yishay

Ссылка скопирована

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi

Do you know what could be the reason for the unstabilty lock ?

Each reset / PWR on/off or FPGA loading get another lock flag value from the SERDES IP port

Yishay

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

You may want to look into the terminations applied to each of the LVDS pins. Also, you can check on the RREF pins. For more details, please refer the Stratix 10 Pin connection guidelines. https://www.intel.com/content/www/us/en/programmable/documentation/lod1484643014646.html#wsh1484644837897

Regards.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

We do not receive any response from you to the previous answer that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you

- Подписка на RSS-канал

- Отметить тему как новую

- Отметить тему как прочитанную

- Выполнить отслеживание данной Тема для текущего пользователя

- Закладка

- Подписаться

- Страница в формате печати