- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm using the 16GB FPGA DDR4 Memory on the Stratix 10 SX SoC Development Kit. When I'm configuring the emif for the FPGA Memory I cannot find the correct timing parameters for the given memory in the development kit. The memory part number is MTA18ASF2G72Hz and the speed bin is -2400. However, the example provided in intel's website (https://www.intel.com/content/www/us/en/products/details/fpga/development-kits/stratix/10-sx.html) is using a memory whose speed bin is -2666. And I cannot find this memory in the provided presets.

Now I'm using the parameters of another memory with the same speed bin in the provided preset, but the timing analyzer is reporting DDR timing issue. Can someone help me by providing the correct configurations for this memory? Since this memory is included in the development kit, I guess there should be some instructions on how to configure it.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adzim,

Thank you for your help. But I cannot open the project since I'm using Quartus Pro 20.1. Can you please share the project in an older version?

Best regards,

Shu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shu,

I'm sorry that I was not aware you were using the Quartus Pro v20.1.

I've created the project in Quartus Pro v20.1 and shared in .qar file.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adzim,

Thank you for your help. Now I'm using the configurations as in your example project. But since my FPGA program is in a diffrerent clock field and has an AXI full interface, I connect my AXI master to the avalon_mm_ctrl port through a avalon clock crossing bridge as shown in the figure. Is that a good choice? If not, what else can I do to cross the different clock field between emif and my FPGA program?

I'm having this question because I'm comparing the read and write speed between the 4GB HPS DDR and the 16GB FPGA DDR on the Stratix 10 board. And the results show that the speed is lower when using FPGA memory. So I'm suspecting the interconnect between AXI and avalon and the clock crossing bridge may increase the total latency. Is that possible?

Thank you,

Shu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adzim,

As a supplement to my previous question, what is the frequency of the user clock in the emif IP? Am I able to change it? If I could change it perhaps I can use this clock in my FPGA program.

Best regards,

Shu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shu,

I think your configuration should be fine.

There is a possibility to cause that when comparing the HPS DDR and FPGA DDR.

The HPS DDR has a circuitry that already been assigned for the EMIF.

But the FPGA DDR can be used any bank that available.

You can make a change on the user clock frequency but it's needs to be in it's range.

Then you have to regenerate the EMIF IP and compile your design.

Please let me know if you have further question.

Thanks,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adzim,

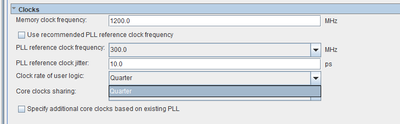

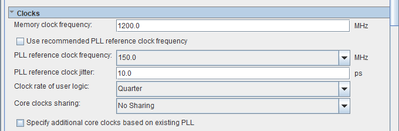

In the IP configurations panel the user clock frequency can only be set to a quarter of the memory clock frequency, so does it mean I should change the memory clock frequency? But in the way I'm wondering:

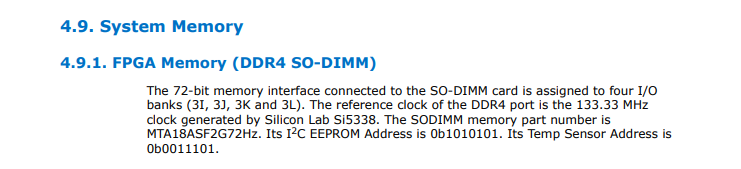

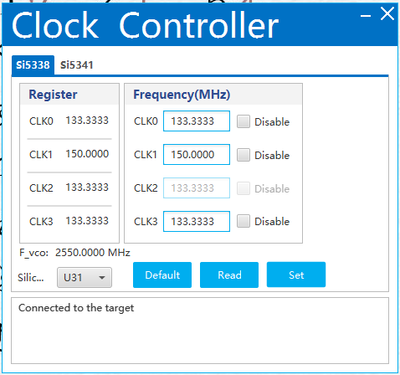

1. In the user manual of the Stratix 10 board it says the 133.3333MHz PLL reference clock is generated by the hardware device Silicon Lab Si5338 on the board. If I change the memory clock frequency I have to change the PLL reference clock frequency at the same time. Is there a way to reconfigure the device to generate a different frequency than 133.3333MHz?

2. If I change the memory clock frequency should I also change the Mem timing parameters?

Thanks,

Shu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shu,

I just review the example design that I've shared before.

I think that the Memory Clock Frequency should be 1200MHz.

You can select the PLL reference clock frequency or you can choose to use the recommended PLL reference clock frequency.

The Mem Timing is based on the Speed Bin and Memory Clock Frequency.

But I think 1200MHz should be the right one.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adzim,

Perhaps I didn't explain my questions clearly, but in your last reply you said I can make a change on the user clock frequency. But in the configuration panel it only allows the user clock frequency to be quarter the memory clock frequency. Then how can I make change to the user clock frequency while keeping the memory clock frequency at 1200MHz? Or I have to change the memory clock frequency at the same time?

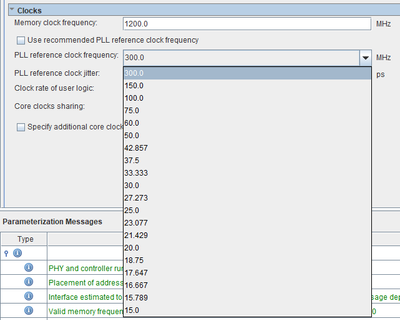

And the PLL reference frequency is also limited in these options. If I set memory clock frequency to 1200MHz then I cannot choose 133.33MHz as PLL reference frequency. Is there a way to reconfigure the Si5338 hardware to get a different frequency?

Thanks,

Shu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shu,

Regarding to the Clock rate of user logic, the clock can only be set to Quarter rate when using the DDR4 interface.

The PLL reference frequency is limited to the options.

You can only choose from the options.

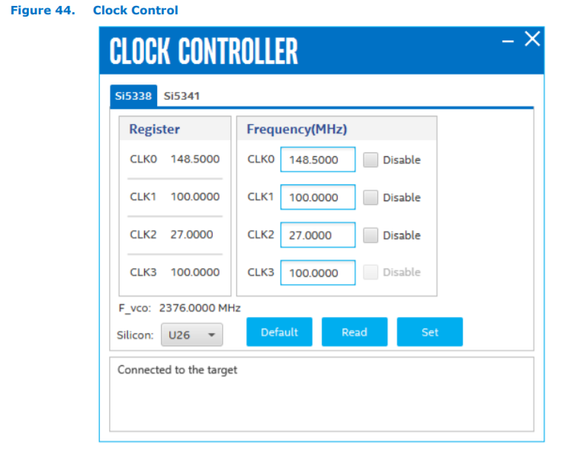

You can reconfigure the Clock in the Clock Controller application.

You need to install the app first.

You need to identify which clock that has been used and then you can change it.

Please let me know if you face any trouble in doing it.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shu,

Do you have any update on this topic?

Thanks,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adzim,

Sorry for my late reply. Now I've set the memory clock frequency to 1200MHz and PLL reference clock frequency to 150MHz.

Then in the clock controller I set CLK1 (which is what I'm using for this emif) to 150MHz, but then I see that the emif is not working: both the local_cal_success and local_cal_fail port are low, and I cannot get access to the memory.

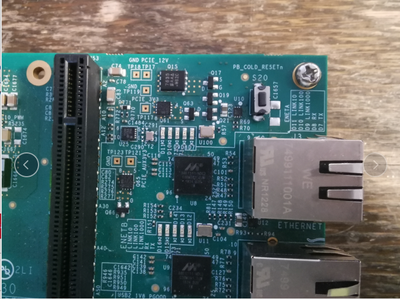

I tried to reset the emif by pressing the nreset button (S20) on the board but the emif cannot get reset. In the qsys file I've connected the local_reset_combiner and the emif like what is done in your example, and the local_reset_req port is connected to the nreset button. Is there anything wrong with my design?

Thank you,

Shu Wang

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shu,

Just for confirmation, have you regenerated the IP and compiled the design after some changes on the EMIF IP?

If you already did, then you can check the pin connection as the Fitter might assigns the pins to different locations.

May I know if the 1066.667MHz example design is working on your board?

The design that I shared to you before.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adzim,

Yes, I've regenerated the IP and compiled the design after I changed the memory clock frequency and PLL reference clock frequency.

The 1066.667MHz example design is working correctly in my design. I've validated it by writing to a certain address and reading it with HPS. So I think the pin connections should be fine.

But since I want to change the user clock frequency (which is fixed at 1/4 memory clock frequency) and use the user clock in my FPGA program, it would be helpful if you can help me figure out why the 1200MHz design is not working.

Thanks,

Shu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shu,

Thank you for your confirmation.

Make sure that the pin locations that have been used in the 1200MHz design is same with the 1066.67MHz.

Is it working if you used 300MHz PLL clock frequency?

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adzim,

I've checked the pin locations and it was same with the 1066.67MHz design.

When I'm using 300MHz PLL clock frequency it works with the default setting (actual reference clock frequency is 133.3333MHz), but after I change the reference clock frequency to 300MHz in the clock controller it stops working. And I have the same problem when I set PLL clock frequency to 150MHz.

I've regenerated the IP files before compiling and I've checked the clock frequency in the generated files. It doesn't seem to be the problem of improperly generated files.

Thanks,

Shu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shu,

I'm glad to hear that the design is working.

Maybe you can use Signal Tap tool to analyze the clock frequency on your board.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Shu,

Do you still have any question on this topic?

If no, then I will put this topic to closure.

Thanks and Regards,

Adzim

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page