- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

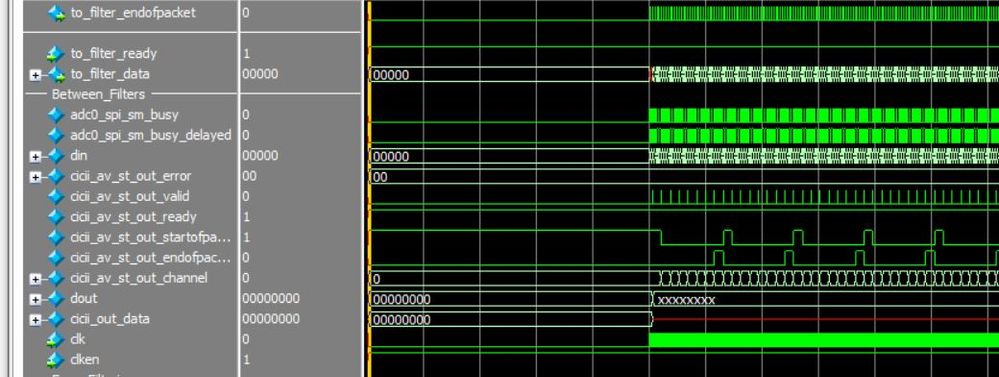

We have built up a QSYS design with our own core feeding into a CIC core, feeding into a FIR core. In our simulation we can see signals and data going into the core, and see the appropriate handshake signals coming out of the core's streaming interface, but the data shows up as unknown! Since it is built with IP, we cannot dive into the core to see where things have gone wrong.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1. What is the device that you are using? 5CSX

2. What is the Quartus version that you are using? 18.1 Standard.

3. Would you mind to further elaborate on the unknown output that you are referring to in the initial description? Some screenshots will be helpful for further understanding.

4. Mind share with me the CIC IP configuration ie .ip file will be helpful.

5. Just wonder if you have had any chance to try simulating the example design generated by the IP to see if the simulation is able to run? ONe of the things on the to do list

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Regarding #5, how did you get the example to simulate. The example design did not include a Do file. I ran the TCL script it had created, but was unsure as to the next step. It would be nice if there was a readme file or other instructions, or did I just miss something.

Here is a screen shot of the waveforms.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Do not close the case! The example design simulates, but the real design does not! We noticed that the example design throughs error codes! We went into the example codes BFM and set the "Forward pressure" variable to False, which disabled the "random" functionality, and caused the SOP and EOF inputs to behave normally, and eliminated the error - IN THE EXAMPLE DESIGN. But we still are not getting data out of the real design, though our SOP and EOF match the example (once random was turned off in the example).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Regarding the errors, they are error codes put out by the core, due to SOP and EOP relationship cased by the FORWARD_PRESSURE defined as "TRUE"

We changed the FORWARD_PRESSURE definition to "FALSE" and the example simulation worked better.

Here is the code from the cicii_example_design_test_program.sv that causes the randomness of the SOP and EOP signals.

fork

begin

while(1) begin

read_input_data_files();

if(`FORWARD_PRESSURE=="TRUE")

begin

src_transaction.idles = ($unsigned($random()) % 10);

end else begin

src_transaction.idles = 0;

end

src_transaction.send_data();

if(source_finished == 0) begin

@(`SRC.signal_min_transaction_queue_size);

end

end

end // source_data_thread

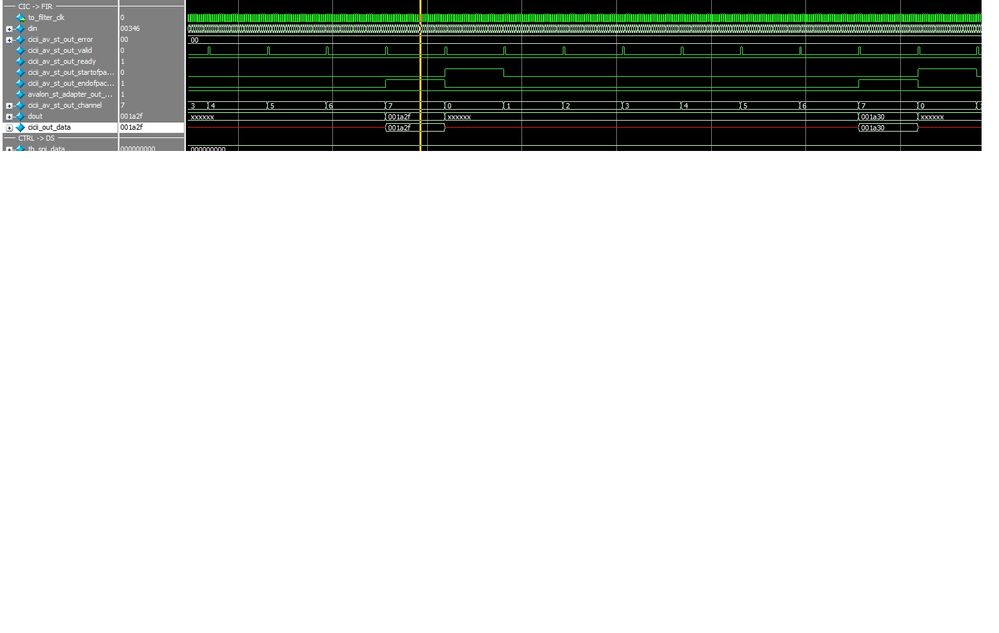

After comparing the two simulations, we noticed differences in the clock rates (ratio between clock frequency and sample rate). After playing with the clock frequency we are now starting to get data out, but only on one channel's time slot.

Can you provide any guidance and/or documentation on setting the clock and sample rates.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Attached is the project with original clocking. Under the simulation directory under C:\Intel_projects\micromeritics\CIC_design\m_293_20091_00_top there is a file mentor.do that will run the simulation. You will need to modify the directory locations in the scripts to match your location, else unzip to something like C:\Intel_projects\micromeritics\CIC_design

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here is the latest waveform that shows data only coming out on channel 7

Some other oddities. Jon has tried to generate test bench for his QSYS design and it fails to generate the TB. I have the same design (older version) and I can generate the test bench without issue. Can you try this on the design that you have.

.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The other thing we are looking at is how the BFMs are being called in the example versus the real design.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes! The initial batch corrupted data coming out of reset was enough to hang the CIC. One simple fix and our design is simulating perfectly. Thank you!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page