- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am currently trying to build a project where a NIOS II needs to communicate with the SDRAM on the Cyclone 10 GX Dev Kit and was wondering what the best way of doing this is.

I have tried connecting together the EMIF IP to the NIOS II processor within Platform Designer but they just complain about the interfaces not aligning. I have managed to get the EMIF IP to talk to a HDL module, but is it necessary to create a custom module to interface between the NIOS II and the SDRAM or is there some pre-existing IP that can connect the NIOS II and SDRAM that I am not aware of?

Many thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can use the Address Span Expander IP in Platform Designer to expand the interface and match it with the NIOS2 CPU and connect them together.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

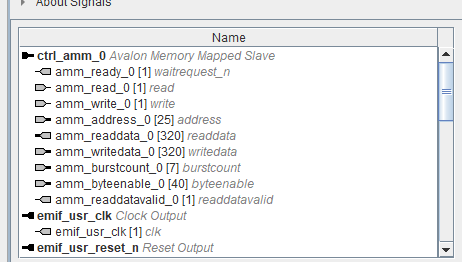

The problem is that the mismatch isn't from the address span but from the datawidths themselves. The EMIF controller has a width of 320 bits, whilst the NIOS2 can only handle 32 bits.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

320? That's a strange width. I'm pretty sure you need a power of 2 or power of 2 plus bits for ECC (if you're using it).

Most dev kits include an example design for the memory that may include a Nios processor or you can generate an example design from the EMIF IP Parameter Editor and connect a Nios to it..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

you have to use the SDRAM controller IP witch will solve all your problems.

https://www.intel.cn/content/dam/altera-www/global/zh_CN/pdfs/literature/hb/nios2/n2cpu_nii51005.pdf

https://www.youtube.com/watch?v=FjuZ3IGNur0

Am I answering your question?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I was digging on the embedded IP peripherals user guide for NIOS II and found this:

“All the IP cores described in this user guide are supported by both Intel® Quartus® Prime Pro Edition and Intel® Quartus® Prime Standard Edition except for the following cores which are only supported by Intel® Quartus® Prime Standard Edition.

- SDRAM Controller Core”

So I looked at the difference between Pro and Standard and the difference is that Pro supports Statix 10, Arria 10 and Cyclone GX 10 and standard supports all the other devices. Looks like SRAM controllers for the latest gen aren’t supported yet. I think this gen has the first hard external memory interfaces so I guess it was a major overhaul. I've seen some reference to testbenches using a NIOS and SDRAM, so I guess is internally developing it. Could Intel confirm if they have something in the works?

In the meantime, what I am trying to do is just build a very basic, low performance SDRAM controller that only has a bust transfer of one and then connect that to the NIOS. The SDRAM half is working fine, but getting it to talk to the NIOS is proving challenging.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page