- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using Quartus II 13.0sp1 (web edition) and need to implement a Cyclone V Native PHY Tranceiver for a Cyclone V GX. When I try and simulate my design with the Native PHY IP core or the Custom PHY IP in the Modelsim-Altera 10.1d Starter Edition, I receive the following error message:

# Loading work.mgt_native(rtl)

# ** Fatal: Error occurred in protected context.

# Time: 0 ps Iteration: 0 Protected: /tb_pll/uut/MGT_1/mgt_native_inst/<protected>/av_xcvr_native_insts[0]/<protected>/<protected>/<protected>/pll[0]/<protected> File: nofile

# FATAL ERROR while loading design

# Error loading design

It appears that this is a known issue and has been flagged in some of the Quartus II software release documentation but never seemed to be fixed. Some of the methods I have already tried:

- using the -novopt option in Quartus II and also manually placing it in the .do file as suggested on these forums

- compiling both the cyclone v verilog and vhdl files instead of only the vhdl files using:

vlog "C:/altera/13.0sp1/quartus/eda/sim_lib/cyclonev_atoms.v" -work cyclonev_ver

vcom "C:/altera/13.0sp1/quartus/eda/sim_lib/cyclonev_atoms.vhd" -work cyclonev

vcom "C:/altera/13.0sp1/quartus/eda/sim_lib/cyclonev_components.vhd" -work cyclonev

- I then add -L cyclonev_ver to the vsim command in the .do file.

None of this has worked and I would love to know if there is a workaround. Implementing these Transceiver cores are difficult enough to understand and will be near impossible without some form of verification.

Is this issue fixed in later releases of Quartus II? Any help is appreciated!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I tried to replicate the issue using Q17.1 Lite Edition & I could able to simulate using ModelSim Intel FPGA starter edition10.5b with the following warning,

# ** Warning: (vsim-3722) <protected>(<protected>): [TFMPC] - Missing connection for port '<protected>'.

Let me check with Quartus II 13.0sp1 (web edition).

Best Regards

Vikas Jathar

(This message was posted on behalf of Intel Corporation)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I can run the examples shown on:

https://fpgawiki.intel.com/wiki/Cyclone_V_Transceiver_PHY_Basic_Design_Examples

They run without a problem in Modelsim 10.1d which makes me think it is Quartus 13.0sp1 that is the problem.. Or I am not designing the Native PHY correctly.

What is the simplest method of getting parallel data from the FPGA to the high speed serializers through the HSMC connectors? I don't need any fancy reset or reconfiguration control - just need to serialize 40-bit parallel data (using the double width setting) at a very high speed. The 40-bit vectors are updated @20MHz (for example) and I need to serialize it @800MHz (40x 20MHz).

Cheers,

Alex

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Alex,

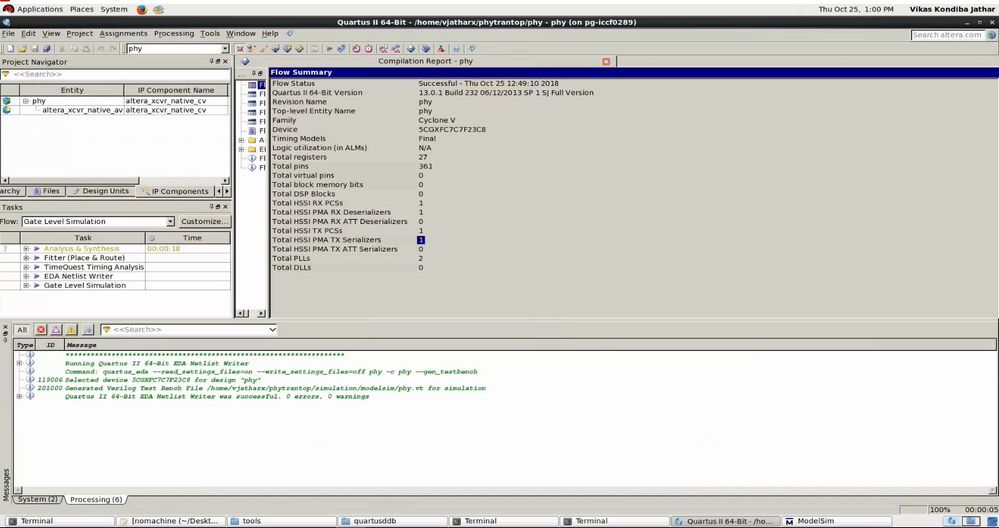

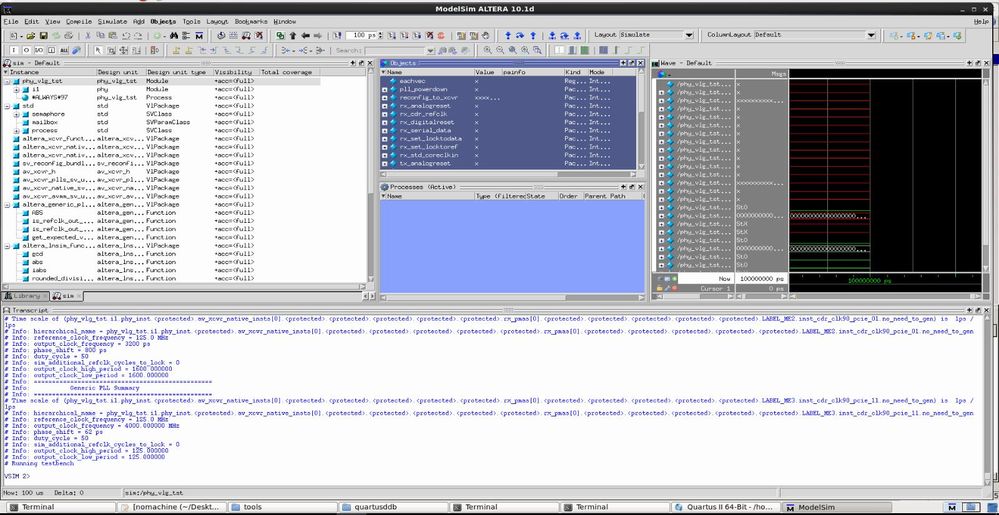

Apologies for the late response. I tried with Quartus II 13.0sp1 (web edition) and Cyclone V Native PHY Tranceiver for a Cyclone V. & simulated successfully with Modelsim-Altera 10.1d Starter Edition.

check screen shots.

Best Regards

Vikas Jathar

(This message was posted on behalf of Intel Corporation)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page