- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

. If anyone can say me how to easily replace this IP I will thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I picked an Verilog Model from manufacturer. This is the only thing that is provided as IP Core from him. This is a file .vp and .v for

NC-Verilog

And I don't know how use as an Qsys component. The main file is the .vp.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello!

For your information, the SDRAM Controller IP is already End Of Life.

If you want to use the IP, you might consider to use older Quartus version such 18.1 and earlier.

Besides, this design was created in Quartus Prime version 17.0.

For better functionality, you need to run it in Quartus version 17.0 as well.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Info (125068): Revision "NIOSDuino" was previously opened in Quartus Prime software version 18.1.0 Lite Edition. Created Quartus Prime Default Settings File C:/Users/Utilizador/Downloads/nios_duino-master/nios_duino-master/contrib/max1000/NIOSDuino_restored/NIOSDuino_assignment_defaults.qdf, which contains the default assignment setting information from Quartus Prime software version 18.1.0 Lite Edition.

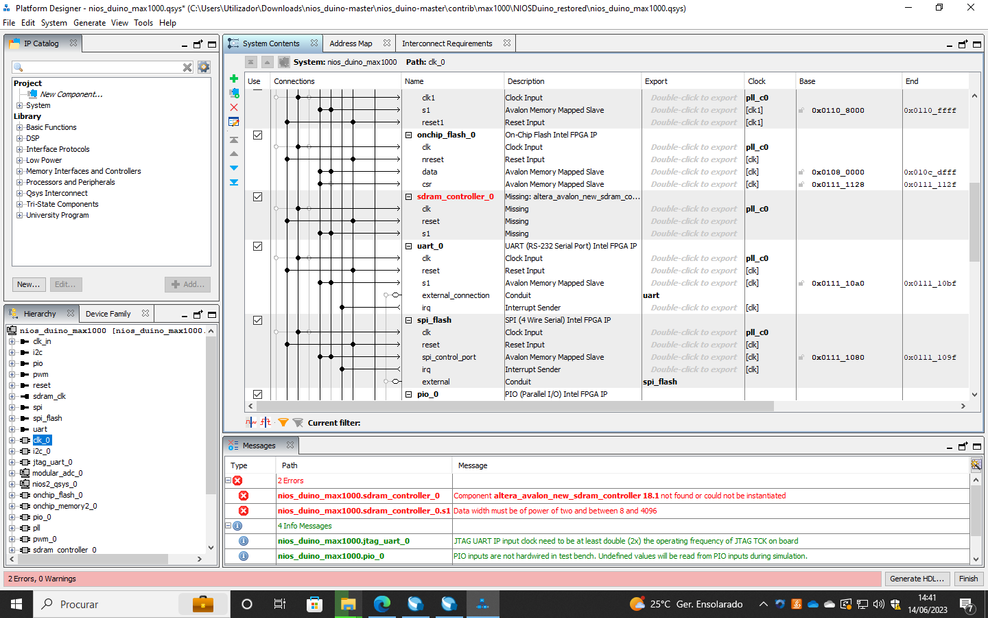

And in the link here is the screenshot of qsys

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I replaced altera_avalon_new_sdram_controller by altera_avalon_onchip_memory2 which has the same pinout. Is this IP Core replacement good (by good, I mean it gives exactly the same result)?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It depends on if the design would work the same whether you are using external memory or onchip memory, since you are making that kind of switch.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well, if you switch the component, you won't be accessing external memory anymore.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I picked an Verilog Model from manufacturer. This is the only thing that is provided as IP Core from him. This is a file .vp and .v for

NC-Verilog

And I don't know how use as an Qsys component. The main file is the .vp.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi dicas3d,

Nios II has been end of lifed. We recommend that you switch to Nios V. Quartus 24.1std is the last version that supports Nios II. You will continue to have difficulties if you design with unsupported IP.

Regards,

Sue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page