- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hello!

I have several emif (ddr4) controllers which everyone have it's own reference clock (from package pin) but I want to feed it from pll when I connect it together and try to implement it I get next error messege (only one is shown):

Error(20181): The permit_cal input port of IOPLL "emif_ed_x7_inst|emif_x32_3|emif_x32_s10_2|arch|arch_inst|pll_inst|pll_inst" is not connected correctly. Enable and export the permit_cal port of downstream IOPLL "emif_ed_x7_inst|emif_x32_3|emif_x32_s10_2|arch|arch_inst|pll_inst|pll_inst" with the Platform Designer GUI and connect to the locked output of upstream IOPLL "u0|iopll_0|stratix10_altera_iopll_i|s10_iopll.fourteennm_pll"

but I do not find where to enable this port in the emif ip...

Can someone help me with this? Or may be advise another solution?

Best regards

링크가 복사됨

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi VMots,

I'm Adzim. Thank you for using the Intel Community.

I've found a KDB for this error message. Link here.

You might need to follow the resolution in there.

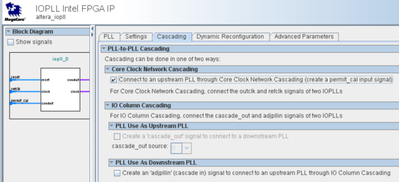

I think you can enable it in the IOPLL IP under the Cascading tab.

I share the screenshot for that.

Please let me know if that helpful.

Thanks,

Adzim

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

I am already see this solution but this is not iopll core but the emif core and it need to have permit_cal input.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

That's for cascading PLLs into each other, not from a PLL to an IP:

Simply turn off the cascading option in the PLL parameters and connect the PLL output to the EMIF clock input. There is no option for a permit_cal input into the EMIF IP because it's not needed.

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

That wasn't a question, how to connect two pll's.

If you have 7 ddr memory controllers in one FPGA it require 14 pins for clock - it is too expensive while one is enough but looks like the intel not give us such possibility.

While you feed ddr memory controllers from plls quartus give you error that you need to connect feedin pll pin with name pll_lock with ddr memory controller pll pin called permit_cal

But permit_cal input is unaccessible from ip configurator

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

No, this is where you use the EMIF core clock sharing option I was asking about originally. You feed the clock to one EMIF and then that EMIF sends the clock to others. Again, there is no permit_cal pin because it's not part of the IP. The option you mention is for cascading PLLs (and just PLLs). From the EMIF parameterization training (https://www.intel.com/content/www/us/en/programmable/support/training/course/omem1122.html):

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

you speaking about core clock network sharing this is not that I need...

I need pll reference clock feeding (pll is inside emif core)

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi VMots,

Do you can share the design with me so that I can replicate the error and debug it?

Thanks,

Adzim

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hello Adzim!

I can share project archive but it too big to share it here .

Thank you

Viktor

- 신규로 표시

- 북마크

- 구독

- 소거

- RSS 피드 구독

- 강조

- 인쇄

- 부적절한 컨텐트 신고

Hi Viktor,

Thanks for sharing the file.

I can see it's the synthesize error.

The Stratix 10 EMIF IP doesn't support PLL cascading as mention in the EMIF User Guide below.

I think you have to reconfigure the PLL reference clock that connect to the EMIF IPs.

Regards,

Adzim