- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Warning (20013): Ignored 16 assignments for entity "IPpll" -- entity does not exist in design

Warning (20014): Assignment for entity set_global_assignment -name IP_TOOL_NAME altera_pll -entity IPpll -sip IPpll.sip -library lib_IPpll was ignored

Warning (20014): Assignment for entity set_global_assignment -name IP_TOOL_VERSION 18.1 -entity IPpll -sip IPpll.sip -library lib_IPpll was ignored

Warning (20014): Assignment for entity set_global_assignment -name IP_TOOL_ENV mwpim -entity IPpll -sip IPpll.sip -library lib_IPpll was ignored

Warning (20013): Ignored 317 assignments for entity "IPpll_0002" -- entity does not exist in design

Warning (20013): Ignored 16 assignments for entity "unnamed" -- entity does not exist in design

Warning (20013): Ignored 14 assignments for entity "unnamed_altclkctrl_0" -- entity does not exist in design

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

"Entity does not exist in design" indicates that you added the IP files to the project but didn't instantiate the PLL in your actual design. Did you instantiate the PLL in your RTL code?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Have built msim_setup.tcl with command lines in sopc_builder with ip-make-simscrpt. Can't find procedures to get these files to incorporate appropriate PLLs in "work" directory with HDL ... getting "failed to run ip-make-simscript" invoking modelsim from quartus...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Len,

Have you linked the ModelSim in Quartus?

what are you using NativeLink/Testbench/Script for simulation?

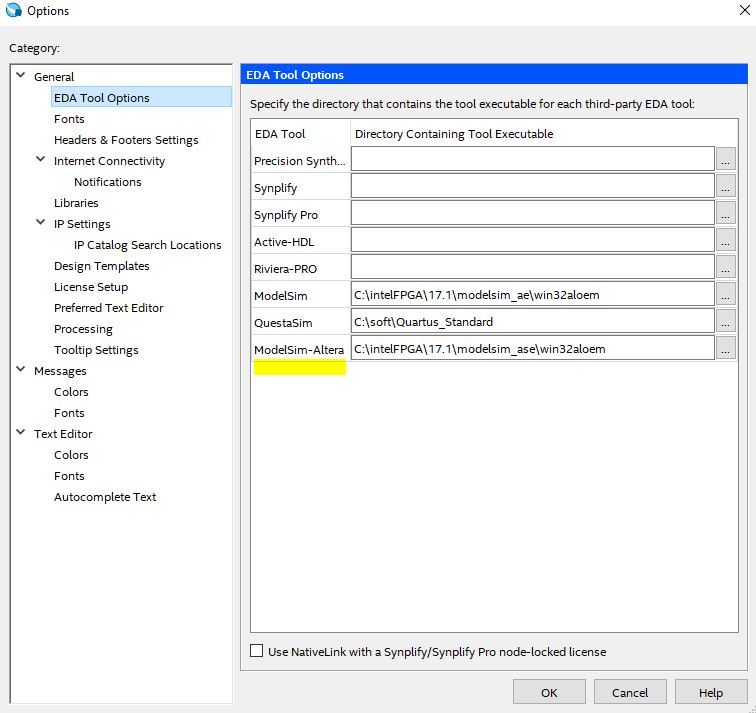

You ca set the path like below,

'Tool' -> 'Options' -> 'EDA Tool Options' ..

C:\intelFPGA\17.1\modelsim_ase\win32aloem

Regards,

Vikas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page