- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi everyone

I'am trying to simulate the LVDS soft IP on MAX10 FPGA using modelsim-altera

it works fine with the receiver but when simuling the transmitter i get those errors

Loading fiftyfivenm.fiftyfivenm_ddio_out(behavior)

# ** Error: (vsim-3033) nofile(38): Instantiation of 'dffeas' failed. The design unit was not found.

# Time: 0 ps Iteration: 0 Instance: /top/ttx/ddio_out/loop0(0)/ddio_outa/inst File: nofile

# Searched libraries:

# C:/Users/alphatec/Desktop/test_sim/lvds_tx2/simulation/modelsim/rtl_work

Thanks for helping

Link copiado

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

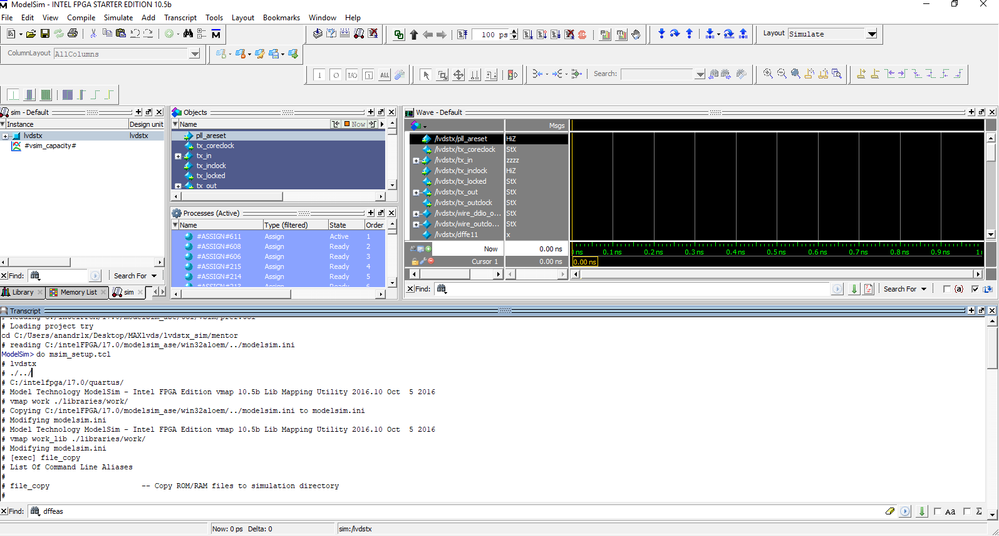

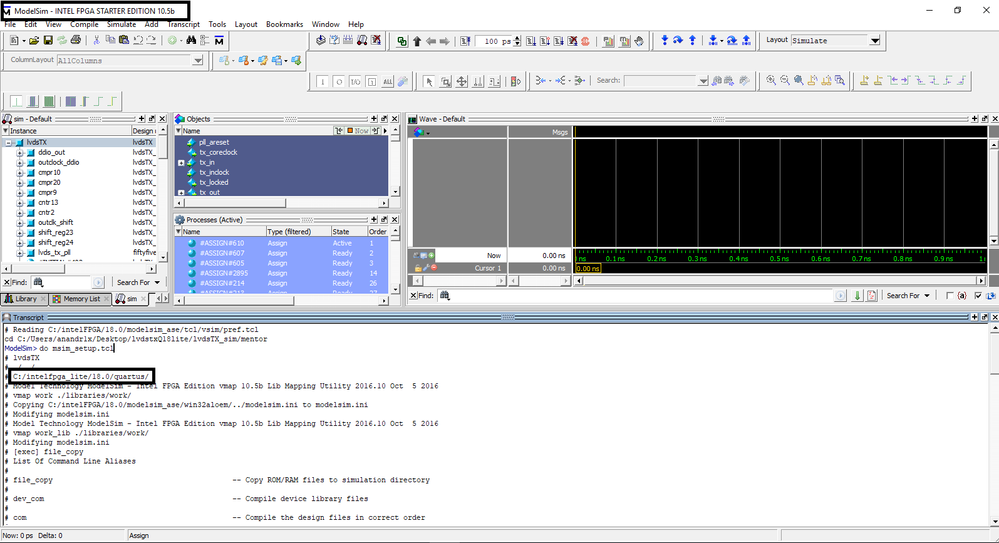

- We have tried to simulate LVDS soft IP on MAX10 FPGA for both receiver and transmitter configuration with other setting being default which worked fine. Attached respective image and Modelsim transcript.

- Used Quartus STD 17.0 & Modelsim 10.5b SE.

Try to regenerate the IP and simulate with appropriate modelsim version based on Quartus version used.

- Can you give more info on Tools used?

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Best Regards,

Anand Raj Shankar

(This message was posted on behalf of Intel Corporation)

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

Thank you for your response.

I tried to regenerate the IP but i got the same problem.

I'm using Quartus prime lite 18.0.0 and ModelSim - INTEL FPGA STARTER EDITION 10.5b.

the settings of the generated IP are:

single supply

mode TX

3 channels

serdes factor 10

external PLL

Best Regards.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

HI,

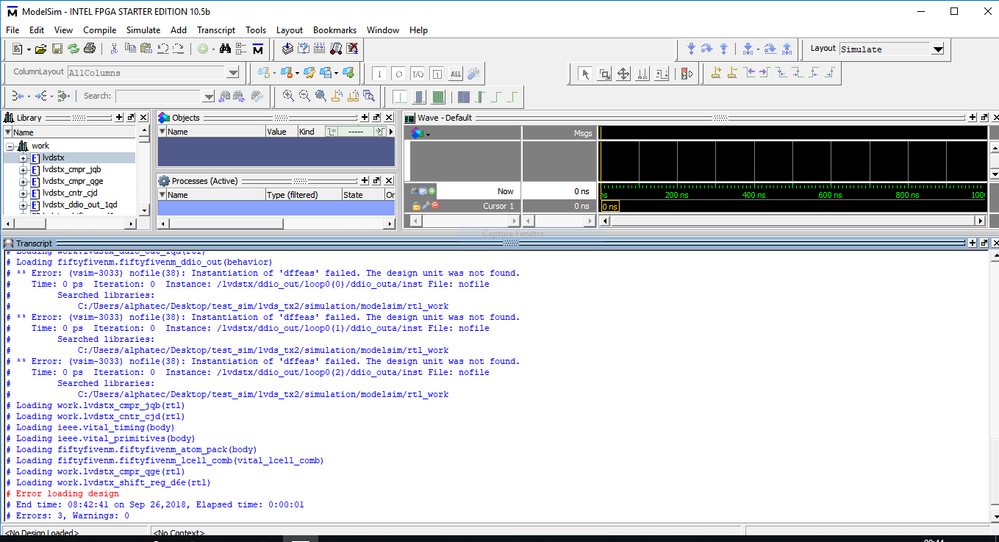

Tried to simulate the IP generated using Quartus 18 lite and Modelsim SE 10.5b.

Not succeeded in producing the error.

But error was replicated on modelsim 10.6c.

Attached transcript and image.

- Reinstall Modelsim from below link and try.

http://fpgasoftware.intel.com/18.0/?edition=lite

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Best Regards,

Anand Raj Shankar

(This message was posted on behalf of Intel Corporation)

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

We acknowledge this issue. Anand as our L1 engineer has replicated this issue and we've posted this in our internal defect database.

Currently, we are in the sighting stage. If there is any progress, I'll let you know.

Thanks,

Joseph

Intel Customer Support

Sales Marketing Group

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi , and thank you again for your response

unfortunately the reinstallation of modelsim didn't resolve the ptoblème .

Best regards.

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

Thanks for continuing provide us your test result. We will revert back this message to our engineering team.

Best Regards,

Joseph

Intel Customer Support

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

Just to let you know we are still working internally with our engineering team. It takes a while for the routing and will keep you posted once we get an updates.

Thanks,

Joseph

Intel Customer Support

- Marcar como novo

- Marcador

- Subscrever

- Silenciar

- Subscrever fonte RSS

- Destacar

- Imprimir

- Denunciar conteúdo inapropriado

Hi,

I have the same error using Quartus Prime 18.1.0 Build 625 9/12/2018 SJ Lite version

and

ModelSim - INTEL FPGA STARTER EDITION 10.5b Revision: 2016.10 Date: Oct 5 2016.

Device: Cyclone10 as on Arduino VIDOR4000 board to be used for students.

Circuit: a simple 7-bit counter.

Log transcript on Modelsim:

# vsim -gui -l msim_transcript -L cyclone10lp_ver -L work testbench

# Start time: 12:07:41 on Jan 06,2019

# Loading work.testbench

# Loading work.prove_project

# Loading cyclone10lp_ver.cyclone10lp_io_obuf

# Loading cyclone10lp_ver.cyclone10lp_io_ibuf

# Loading cyclone10lp_ver.cyclone10lp_lcell_comb

# ** Error: (vsim-3033) prove_project.vo(1998): Instantiation of 'dffeas' failed. The design unit was not found.

# Time: 0 ps Iteration: 0 Instance: /testbench/pproj File: prove_project.vo

# Searched libraries:

# C:/intelFPGA/18.1/modelsim_ase/altera/verilog/cyclone10lp

# D:/PROGETTI/ARDUINO/Vidor4000/projects/prova/simulation/modelsim/gate_work

Thanks for the help.

Fabio

- Subscrever fonte RSS

- Marcar tópico como novo

- Marcar tópico como lido

- Flutuar este Tópico para o utilizador atual

- Marcador

- Subscrever

- Página amigável para impressora