- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm trying to add weak pull-ups on JP7 GPIO1 of DE10-nano board.

The board boots to Linux so as far as I understand FPGA image is loaded by Uboot from the rbf file on boot partition.

There is a Default FPGA project provided with DE10-nano, however, GPIO pins are not assigned in this project.

What am I missing here? Is this the correct project? Which settings map between Cyclone pins and GPIO accessed by HPS and how to modify them to enable weak pull-ups?

Thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello ,

you can include in two ways ;

i) use the qsf assignment tcl script to add pull up as smillar to the FPGA.

ii) or you can use the pin planner

iii) or you can use the assignment editor

Here is the document i got through google which include picture by picture

https://sites.ualberta.ca/~delliott/ece492/appnotes/2013w/GPIO_internal_pullup_resistor/AppNote_GPIO_Internal_Pullup_Resistor.pdf

Thank you ,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sree

I found a project on DE10-nano CD (in \Demonstrations\FPGA\Default). The board User Manual refers to this project as manufacturer default.

It has all the GPIO pins and adding pull-ups is quite straight forward in Quartus.

When I compile it and convert SOF to RBF file for U-Boot to load, U-Boot fails to load device tree (I get ERROR: Did not find a cmdline Flattened Device Tree message via COM port) although the same device tree file is in the same place on SD card.

Does creating RBF for DE10-nano requires any special steps?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello there ,

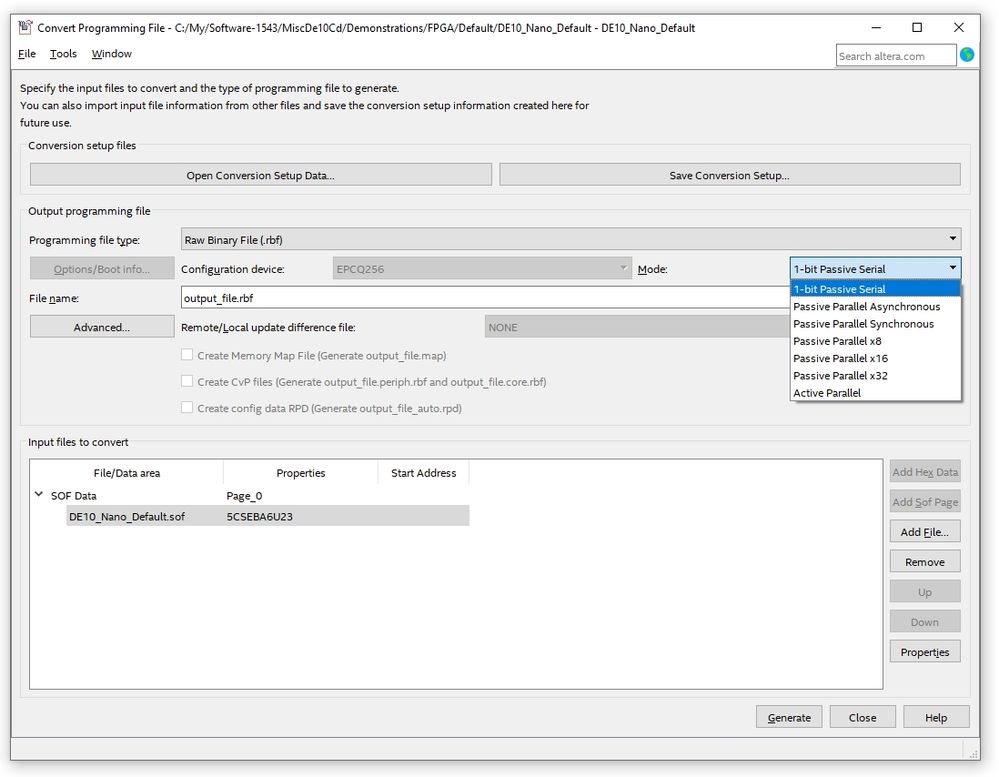

yeah , In the quartus software ; menu bar -?> File -> Converting programming files -> select RBF and also select the which way device are connected to hps

i.e active serial x1 or 4 and add the sof and click convert.

Thank you ,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sree,

there is no active serial option for RBF file. Please, see the attached screenshot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I could see active serial on my PC in my quartus installation, Can i know device you using and quartus version ?

Thank you ,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Also you saying when you boot up you are getting the device tree error ? can you use the image given by the terasic package , Kindly dont change anything and try to boot it

Thank you ,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm compiling with Quartus Prime 18.1. My SD card is the original one which came with DE10-nano and the only file I change is RBF.

By the way, if in case of Linux boot HPS configures FPGA shouldn't I use passive mode? This is what I understand from https://www.intel.com/content/www/us/en/programmable/support/support-resources/support-centers/devices/cfg-index/cfg-compare.html

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

yes you are correct , you should use the passive x mode ; sorry for confusion ;

Thank you ,

Regards

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I generated in Passive Parallel x16 RBF, set MSEL DIP switch to all-ON as required by DE10-nano manual and I have the same situation: FPGA is loaded (orange LED is ON, green LEDs are blinking) but U-Boot complains about missing device tree:

append: root=/dev/mmcblk0p2 rootwait mem=0x3F000000 memmap=16M$0x3F000000 ttyS0,115200

ERROR: Did not find a cmdline Flattened Device Tree

Could not find a valid device tree

SCRIPT FAILED: continuing...

reading /socfpga_cyclone5_de10_nano.dtb

29940 bytes read in 9 ms (3.2 MiB/s)

Also seems confusing to me that right after Did not find message there is reading /socfpga_cyclone5_de10_nano.dtb which means the device tree is really there on SD card.

Another strange issue is that DE10-nano boots Linux with MSEL switch set to ON-OFF-ON-OFF which means Passive Parallel x32 mode but Quartus conversion program does not allow 32 bit mode showing the following error: Device 5CSEBA6U23 does not support Passive Parallel x32 scheme.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

from my understanding error is not saying it is not finding the device tree ... Error " Did not find the cmdline flattened device tree "

can you check the sysid you set in the sof and device tree both are same ?

Thank you,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I cannot find sysid in the Default project provided with DE10-nano CD.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sree

I cannot find sysid anywhere in the Default FPGA project. Can you, please, guide me how to find it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello..Sure..so you are using the same file what given by the terasic and still you are getting the dtb file error right ?

or you modified anything there ?

Thank you ,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'd like to describe step-by-step what I did to make sure I worked with correct files.

I download DE10-Nano CD-ROM version 1.3.7 from www.terasic.com.tw

I extracted CD-ROM contents and opened Demonstrations\FPGA\Default\DE10_Nano_Default.qpf in Quartus 15.1 (the same version as appears in qpf file)

I compiled the project without any modifications

I converted the compiled SOF to Passive Parallel x16 RBF

I put the new RBF on the original SD card which came with DE10-nano in place of the original RBF

After reboot I got the error described above

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I just downloaded the nano-CD-ROM version 1.3.7 and I looked into qsf file ....

Looks like last quartus version used is 16.0.2 not the 15.1. There might be chance you were using original quartus verison which can be used by tersasic to create the project.

Can you use the 16.0.2 ?

Here is another question i got , what is the size of rbf compare to package came with builded rbf ?

Thank you ,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I compiled 1.3.7 Demonstrations\FPGA\Default\DE10_Nano_Default.qpf in Quartus 16.1 and converted the SOF to RBF trying different formats. The file sizes I got:

7,007,204 1-bit-passive-serial.rbf

7,007,184 passive-parallel-async.rbf

7,007,184 passive-parallel-sync.rbf

7,007,204 passive-parallel-x16.rbf

7,007,204 passive-parallel-x8.rbf

The original de10-nano.rbf which comes on DE10-nano SD card is only 3,368,700 bytes.

The CD contains several RBFs in projects other than Default but none of them matches the size of de10-nano.rbf:

1,971,208 Demonstrations/FPGA/DDR3_RTL/demo_batch/soc_system.rbf

1,971,208 Demonstrations/FPGA/DDR3_RTL/soc_system.rbf

2,164,212 Demonstrations/FPGA/DDR3_VIP/demo_batch/soc_system.rbf

2,165,948 Demonstrations/FPGA/DDR3_VIP/soc_system.rbf

2,202,852 Demonstrations/SoC_FPGA/ControlPanel/Quartus/output_files/soc_system.rbf

2,199,000 Demonstrations/SoC_FPGA/DE10_NANO_SoC_FB/output_files/soc_system.rbf

2,081,456 Demonstrations/SoC_FPGA/DE10_NANO_SoC_GHRD/output_files/soc_system.rbf

2,516,264 Demonstrations/SoC_FPGA/Nios_Access_DDR3/demo_batch/soc_system.rbf

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok...t , now i think i got the issue you facing ,

Actually you need to enable the compression option in the Quartus while converting the file into rbf .

Convert programming files -> click the sof -> properties-> click the compression check box

Can you try and let me know how it go ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I created passive parallel x16 RBF with compression.

The file size is 2.5MB vs original file's 3.3MB

FPGA programming OK: orange LED is on, green ones are blinking

But Linux boot still fails:

reading /extlinux/../zImage

5478000 bytes read in 375 ms (13.9 MiB/s)

append: root=/dev/mmcblk0p2 rootwait mem=0x3F000000 memmap=16M$0x3F000000 ttyS0,115200

ERROR: Did not find a cmdline Flattened Device Tree

Could not find a valid device tree

SCRIPT FAILED: continuing...

reading /socfpga_cyclone5_de10_nano.dtb

29940 bytes read in 9 ms (3.2 MiB/s)

starting USB...

USB0: Core Release: 2.93a

dwc_otg_core_host_init: Timeout!

...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok..thank you for the update;

Can you load the file which is provided by terasic and try to boot ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When I change my RFB with the original one from Terasic it boots fine.

Not sure if it helps, but I'd like to note that the LED pattern of the CD Default project and Terasic RBF is different:

Default project RBF (from CD) continuously switches between LEDs 1,3,5,7 and 0,2,4,6.

Terasic RBF (from SD card) briefly blinks LEDs 0,1,2,3,4,5,6,7 after boot and then only dowble-blinks user LED approx. one a second.

So I guess we are dealing here not only with RBF format/loading issue but also with different VHDL designs.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page