- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I design the Max10m02scu169i7 by the Quartus (Quartus Prime 17.1) Lite Edition,but when I change a parameter in my project,my work didn't work well anymore,as long as I change the parameter back to the previous value,the work does all well.

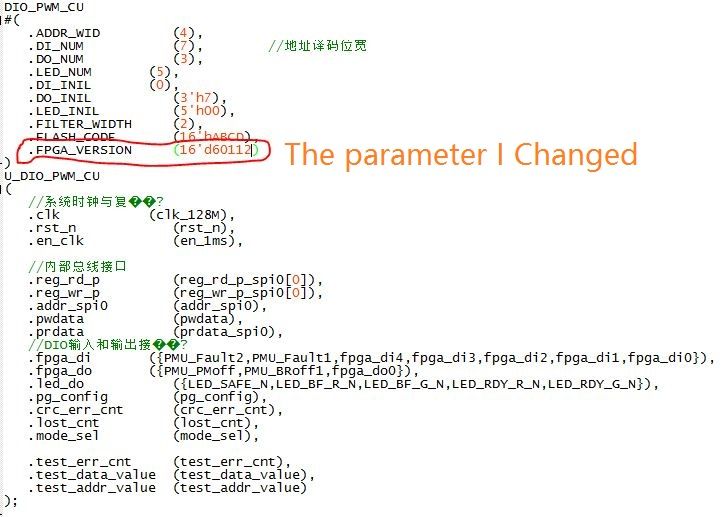

The parameter which I changed is just a FPGA soft version defined as "parameter".And I make sure there is no warnings in TimeQuset.

I try to use another standard version of Quartus do the same operations above ,and there is no problem occurs.

So,I want to know what's the diffrent of Lite Edition and Standard Edition?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you provide code or info about the parameter you are talking about?

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok,thank you

There are about two modules in my project,a module of serial communication and a parallel data bus interface to my DSP.

When I changed the parameter "FPGA_VERSION" from "16'd60112" to "16'd112",then another module in my project did't work well,by the way ther are no busyness between the two modules,as well as I change it back ,then all is well.But if I use the standard version of Quartus,the same problem won't happen.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Without knowing what affect the parameter has on the other module, there's no way to really figure out what's going on here. The only thing I can think of is that 60112 requires all 16 bits (0xEAD0) while 112 only requires 8 bits (really only 7 bits; 0x70). So perhaps some type of optimization for this is different between Lite and Standard, though I doubt it. More info is needed. What is not working well with the changed parameter value?

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your help!

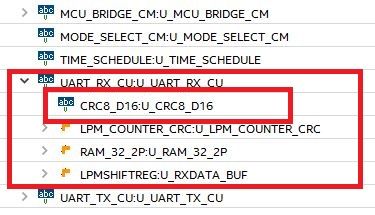

There is a CRC check in my serial communication receive module ,the CRC will be always wrong when I change the parameters "FPGA_VERSION".And I make sure there are not any connections between the two modules.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So perhaps the upper 8 bits are getting optimized away and that affects the operation of the CRC? Not sure without seeing the code.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Quartus Comparison: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/po/ss-quartus-comparison.pdf

Not able to debug for now without seeing the code/design. Advise using Quartus Standard Edition if the problem still persists.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page