- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Greetings,

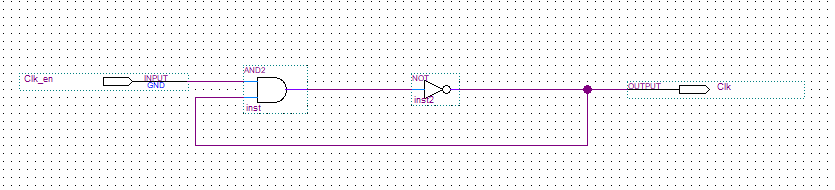

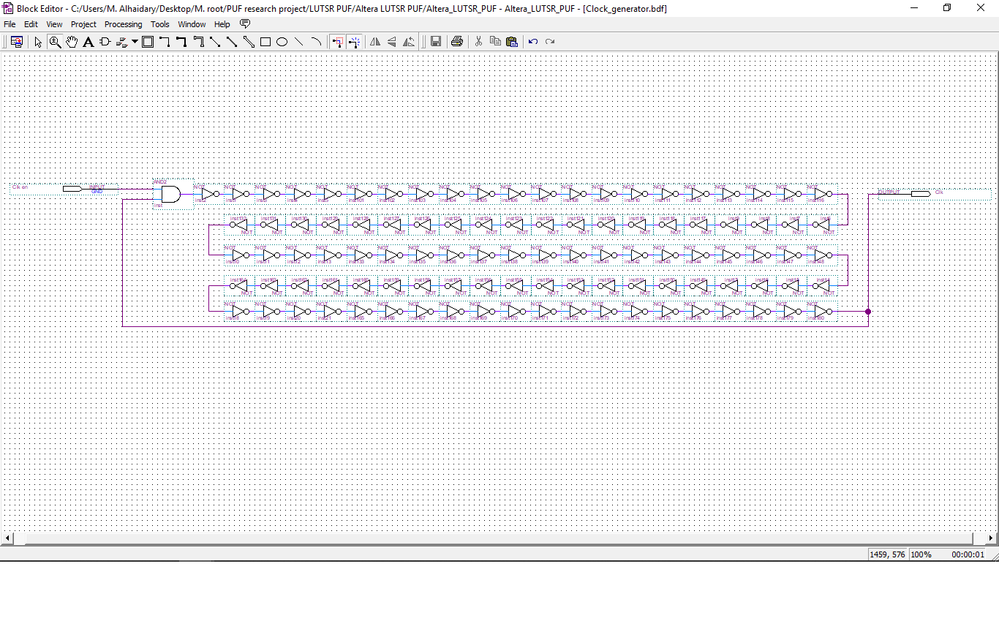

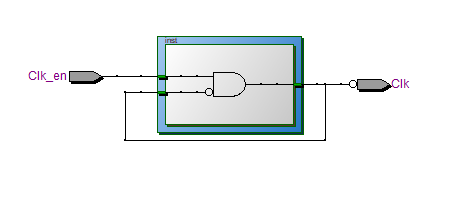

I'm trying to implement a simple clock generator design using Quartus II web version 11.1:

However when I configured it onto my Cyclone II DE2 FPGA, it gave me a 0 output when I set the Clk_en input.

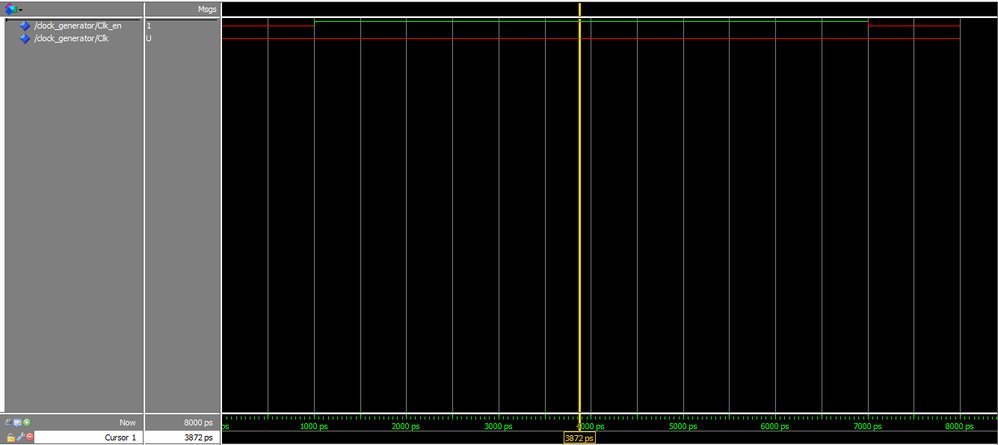

I then tried to simulate it using ModelSim, and it turned out to give me an undefined output:

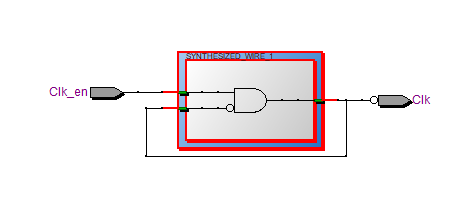

Even though my tech. map viewer is giving me the correct circuit:

How can I fix this issue and get a clock signal on the output?

Thank you in advance,

Best regards.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you check by varying 'Clk_en' input?

Instead of keeping it up high.

what exactly are you trying to do?

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Best Regards

Vikas Jathar

(This message was posted on behalf of Intel Corporation)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

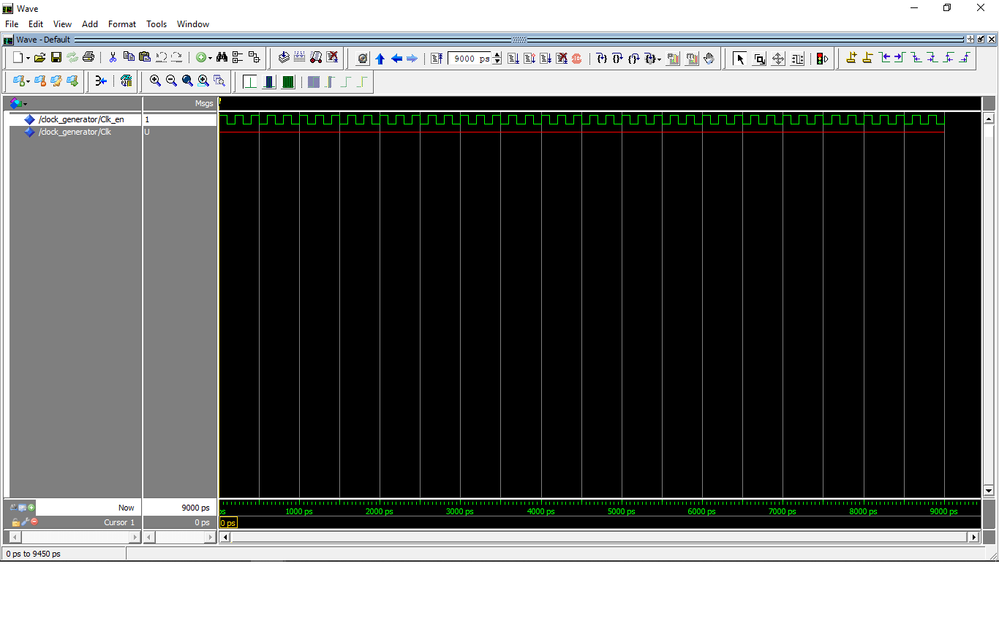

I tried your suggestion but with no success:

I'm trying to design a clock generator that I'll be able to manually adjust its period.

Your help is greatly appreciated, any other suggestion?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The simulator doesn't take into gate delays so it won't model the oscillation that is based on the gate delay. When running this in hardware - trying stringing many inverters (100?) in a row so that the circuit has a chance to meet the VIH/VIL switching threshold. Make sure the compiler doesn't gobble up all the delay (check the fit report) on how many LUTs is uses.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I did your suggestion, below are about 120 inverters:

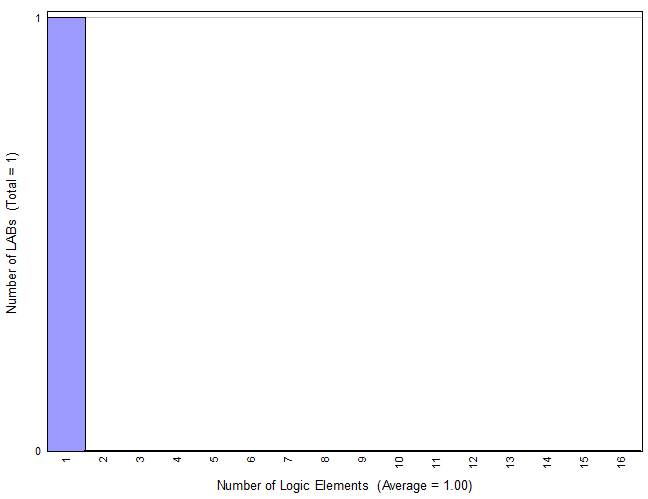

But the compiler is washing them away:

How can I prevent that from happening so that I can implement it on hardware?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here is a thread that discusses this: https://forums.intel.com/s/question/0D50P00003yyP6gSAE/how-to-turn-off-the-optimization-that-removes-repeated-logic

Let us know how that works!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So I replaced the long chain of inverters with a long chain of LCELL primitives, and the tech. viewer is showing them correctly without washing them away, when I implement the design on hardware, and enable the Clk_en input, the LED lights up fadely, does this mean that the clock is working but oscillating too fast for the eye? If so then how do I measure the period of one clock cycle?

Thank you in advance,

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm still eager to solve this issue so that I can progress forward with my project. Any help is appreciated.

How can I measure the period of one clock cycle in the above situation so that I'll be able to manually control it with my delay elements?

Thank you in advance,

Best regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

If you want a clock that can be used in a testbench, and that does work properly you can use someting link this (file.VHD):

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity DE10_STD_CLK_BENCH is

end entity;

architecture arch_DE10_STD_CLK_BENCH of DE10_STD_CLK_BENCH is

constant F_Clock : real :=50000000.0;

signal T_CLK : time :=1.0/F_Clock * 1sec;

signal CLOCK_50 : std_logic:='0';

begin

main_clock: process

begin

CLOCK_50<='1' after T_CLK / 2, '0' after T_CLK;

wait until CLOCK_50='0';

end process;

END architecture;

Best Regards,

Johi.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

There are a number of ways to check the clock frequency. Probably the simplest would be to take the output of the oscillator circuit you created and run into a large counter (I suggest 64 bits). You can generate this circuit block in the IP Megawizard – just select 64bits and binary output, use defaults for other settings.Take each output bit of the counter and run into a large Multiplexer. Use the switches as the selects to the multiplexer (6 bits for select) and attach the output of the multiplexer to an LED. Take 2 more LEDs and just make them a “1” or “0” (one of them will be on permanently after programming the board). Program the board. If the LED attached to the clock is half as bright as the one that is permanently on, then the tap from the multiplexer is too low of a bit from the counter and its switching and is blinking too fast for you to see. Keeping trying different bits of the counter until the LED attached to the divided clock blinks at a rate of about 10 seconds on and 10 seconds on and do the math to figure out what frequency the oscillator is blinking at. I built this circuit based on this wiki post and it worked for me (no gate eating!): https://fpgawiki.intel.com/wiki/Ring_Oscillator

If you need my archive file of this design, let me know (Verilog).

Cheers,

Larry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If you have accessto an oscilloscope you might be able to probe the led (or a gpio pin) which givesyou a more acurate reading. If your signal is too fast for the scope you'll need the counter solution to scale the clock to a slower signal.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page