链接已复制

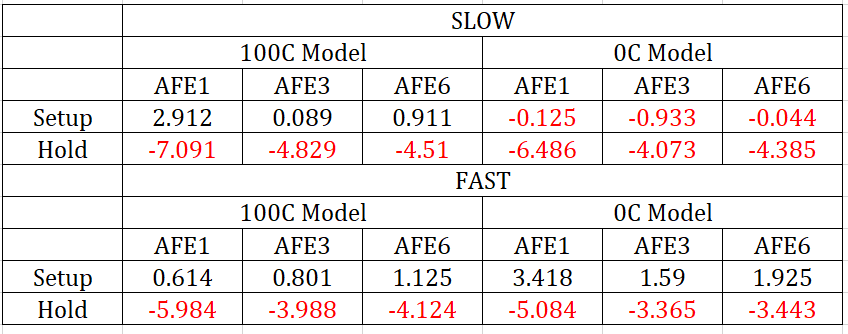

This is one time run result. I use PLL phase in SDC file to adjust the timing result, but never succed. Hold time even is larger than 3.571ns(280MHz). I don't know how to satisfy the timing . Is there anything else i forget to do with my SDC file?

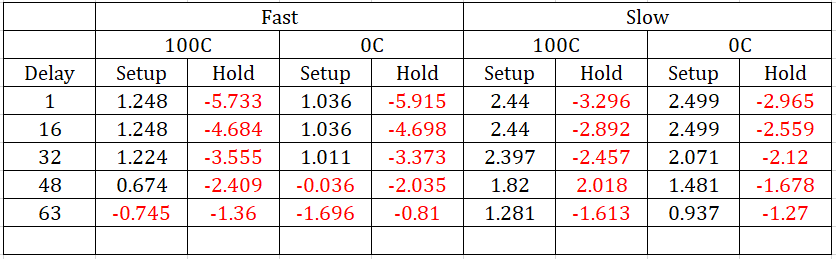

If DDIO sample with the input clock from pin, and I change the data time delay from pin to DDIO input use INPUT_DELAY_CHAIN in .QSF file, hold time is never satisfied. The result is below

Hi ,I am a colleague of ljian50, pls see AFE5809 datasheet section 7.10 and 8.3.8 for LVDS time requirements. (https://www.ti.com.cn/lit/ds/symlink/afe5809.pdf?ts=1591957198622&ref_url=https%253A%252F%252Fwww.ti.com.cn%252Fproduct%252Fcn%252FAFE5809)

We heard that A10 IC have some problem related to silicon and can not close the timing for DDIO, but not sure if this is true.

@KhaiY_Intel I noticed you answered on a similar question some months ago, would you pls also help take a look on this question? Thanks!

https://forums.intel.com/s/question/0D50P00004Q8inFSAR/using-ddioin-to-read-adc-data-and-timing-analysis